# CMOS 32-BIT SINGLE CHIP MICROCOMPUTER S1C33L03 Technical Manual

S1C33L03 PRODUCT PART S1C33L03 FUNCTION PART

# S1C33L03 Technical Manual

This manual describes the hardware specifications of the Seiko Epson original 32-bit microcomputer S1C33L03.

#### S1C33L03 PRODUCT PART

Describes the hardware specifications of the S1C33L03 except for details of the peripheral circuits.

## S1C33L03 FUNCTION PART

Describes details of all the peripheral circuit blocks for the S1C33 Family microcomputers.

Refer to the "S1C33000 Core CPU Manual" for details of the S1C33000 32-bit RISC CPU.

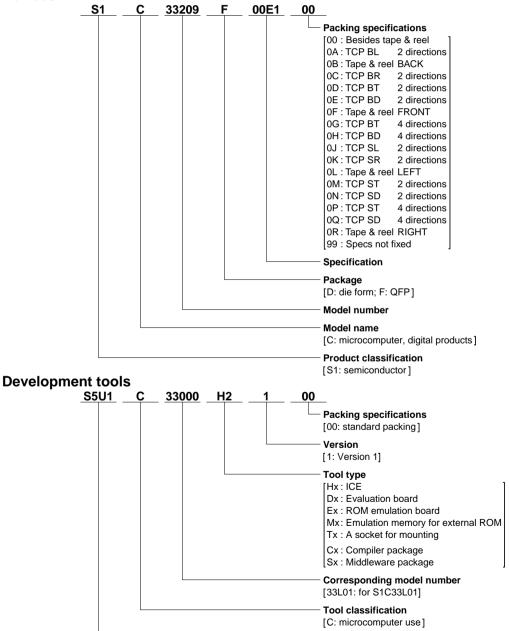

## Configuration of product number

#### **Devices**

**Product classification**

[S5U1: development tool for semiconductor products]

# S1C33L03 PRODUCT PART Table of Contents

| 1 | Outline                                                              |                                                                                                                                                                                                                                                                                                                                                                                                              | A-1                                  |

|---|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

|   | 1.1                                                                  | Features                                                                                                                                                                                                                                                                                                                                                                                                     | A-1                                  |

|   |                                                                      | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                |                                      |

|   | 1.3                                                                  | Pin Description                                                                                                                                                                                                                                                                                                                                                                                              |                                      |

|   |                                                                      | 1.3.1 Pin Layout Diagram (plastic package)                                                                                                                                                                                                                                                                                                                                                                   |                                      |

|   |                                                                      | 1.3.2 Pin Functions                                                                                                                                                                                                                                                                                                                                                                                          |                                      |

| 2 |                                                                      | Supply                                                                                                                                                                                                                                                                                                                                                                                                       |                                      |

|   |                                                                      | Power Supply Pins                                                                                                                                                                                                                                                                                                                                                                                            |                                      |

|   |                                                                      | Operating Voltage (VDD, VSS)                                                                                                                                                                                                                                                                                                                                                                                 |                                      |

|   |                                                                      | Power Supply for I/O Interface (VDDE)                                                                                                                                                                                                                                                                                                                                                                        |                                      |

| _ |                                                                      | Power Supply for Analog Circuits (AVDDE)                                                                                                                                                                                                                                                                                                                                                                     |                                      |

| 3 |                                                                      | Memory                                                                                                                                                                                                                                                                                                                                                                                                       |                                      |

|   |                                                                      | ROM and Boot Address                                                                                                                                                                                                                                                                                                                                                                                         |                                      |

|   |                                                                      | RAM                                                                                                                                                                                                                                                                                                                                                                                                          |                                      |

| 4 | Periphe                                                              | eral Circuits                                                                                                                                                                                                                                                                                                                                                                                                | A-16                                 |

|   |                                                                      | List of Peripheral Circuits                                                                                                                                                                                                                                                                                                                                                                                  |                                      |

|   | 4.2                                                                  | I/O Memory Map                                                                                                                                                                                                                                                                                                                                                                                               | A-17                                 |

| 5 | Power-                                                               | Down Control                                                                                                                                                                                                                                                                                                                                                                                                 | A-65                                 |

| 6 | Basic E                                                              | xternal Wiring Diagram                                                                                                                                                                                                                                                                                                                                                                                       | A-68                                 |

| 7 | Precau                                                               | tions on Mounting                                                                                                                                                                                                                                                                                                                                                                                            | A-69                                 |

| 8 | Electric                                                             | al Characteristics                                                                                                                                                                                                                                                                                                                                                                                           | A-71                                 |

|   | 8.1                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                              |                                      |

|   |                                                                      | Absolute Maximum Rating                                                                                                                                                                                                                                                                                                                                                                                      | A-71                                 |

|   | 8.2                                                                  | Absolute Maximum Rating                                                                                                                                                                                                                                                                                                                                                                                      |                                      |

|   |                                                                      | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                     | A-72                                 |

|   | 8.3<br>8.4                                                           | Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                             | A-72<br>A-73<br>A-75                 |

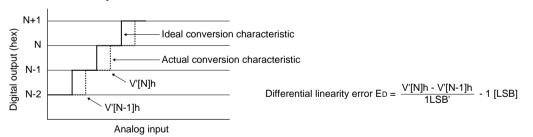

|   | 8.3<br>8.4<br>8.5                                                    | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics                                                                                                                                                                                                                                                                                                     | A-72<br>A-73<br>A-75<br>A-76         |

|   | 8.3<br>8.4<br>8.5                                                    | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics                                                                                                                                                                                                                                                                                 | A-72<br>A-73<br>A-75<br>A-76         |

|   | 8.3<br>8.4<br>8.5                                                    | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics  8.6.1 Symbol Description                                                                                                                                                                                                                                                       | A-72<br>A-73<br>A-75<br>A-76<br>A-78 |

|   | 8.3<br>8.4<br>8.5                                                    | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics  8.6.1 Symbol Description  8.6.2 AC Characteristics Measurement Condition                                                                                                                                                                                                       |                                      |

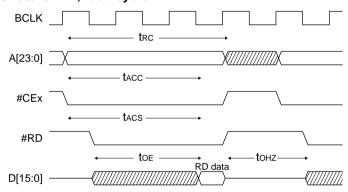

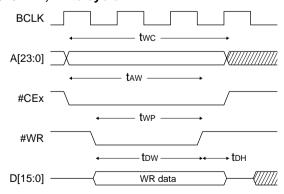

|   | 8.3<br>8.4<br>8.5                                                    | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics  8.6.1 Symbol Description  8.6.2 AC Characteristics Measurement Condition  8.6.3 C33 Block AC Characteristic Tables                                                                                                                                                             |                                      |

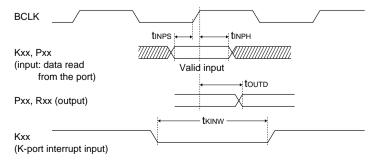

|   | 8.3<br>8.4<br>8.5                                                    | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics  8.6.1 Symbol Description  8.6.2 AC Characteristics Measurement Condition  8.6.3 C33 Block AC Characteristic Tables  8.6.4 C33 Block AC Characteristic Timing Charts                                                                                                            |                                      |

|   | 8.3<br>8.4<br>8.5<br>8.6                                             | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics  8.6.1 Symbol Description  8.6.2 AC Characteristics Measurement Condition  8.6.3 C33 Block AC Characteristic Tables  8.6.4 C33 Block AC Characteristic Timing Charts  8.6.5 LCD Interface AC Characteristics                                                                    |                                      |

|   | 8.3<br>8.4<br>8.5<br>8.6                                             | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics  8.6.1 Symbol Description  8.6.2 AC Characteristics Measurement Condition  8.6.3 C33 Block AC Characteristic Tables  8.6.4 C33 Block AC Characteristic Timing Charts                                                                                                            |                                      |

| 9 | 8.3<br>8.4<br>8.5<br>8.6                                             | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics  8.6.1 Symbol Description  8.6.2 AC Characteristics Measurement Condition  8.6.3 C33 Block AC Characteristic Tables  8.6.4 C33 Block AC Characteristic Timing Charts  8.6.5 LCD Interface AC Characteristics  Oscillation Characteristics                                       |                                      |

| 9 | 8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>Packag                     | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics  8.6.1 Symbol Description  8.6.2 AC Characteristics Measurement Condition  8.6.3 C33 Block AC Characteristic Tables  8.6.4 C33 Block AC Characteristic Timing Charts  8.6.5 LCD Interface AC Characteristics  Oscillation Characteristics  PLL Characteristics                  |                                      |

|   | 8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br><b>Packag</b><br>9.1       | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics  8.6.1 Symbol Description  8.6.2 AC Characteristics Measurement Condition  8.6.3 C33 Block AC Characteristic Tables  8.6.4 C33 Block AC Characteristic Timing Charts  8.6.5 LCD Interface AC Characteristics  Oscillation Characteristics  PLL Characteristics  Plastic Package |                                      |

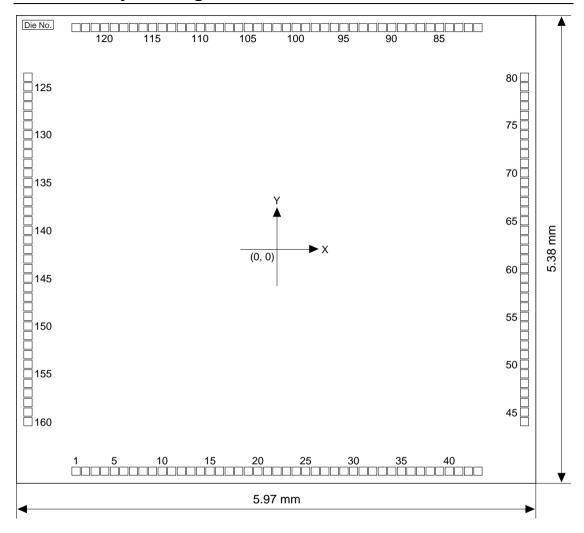

|   | 8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>Packag<br>9.1<br>9 Pad Lay | Recommended Operating Conditions  DC Characteristics  Current Consumption  A/D Converter Characteristics  AC Characteristics  8.6.1 Symbol Description  8.6.2 AC Characteristics Measurement Condition  8.6.3 C33 Block AC Characteristic Tables  8.6.4 C33 Block AC Characteristic Timing Charts  8.6.5 LCD Interface AC Characteristics  Oscillation Characteristics  PLL Characteristics                  |                                      |

## TABLE OF CONTENTS

| Appendix | A < Reference > External Device Interface Timings | A-113 |

|----------|---------------------------------------------------|-------|

| A.1      | DRAM (70ns)                                       | A-114 |

| A.2      | DRAM (60ns)                                       | A-117 |

| A.3      | ROM and Burst ROM                                 | A-121 |

| A.4      | SRAM (55ns)                                       | A-123 |

| A.5      | SRAM (70ns)                                       | A-125 |

| A.6      | 8255A                                             | A-127 |

| Annendix | B Pin Characteristics                             | Δ-128 |

# S1C33L03 FUNCTION PART Table of Contents

| I (  | OUTLINE                                       |           |

|------|-----------------------------------------------|-----------|

| I-1  | INTRODUCTION                                  | B-I-1-1   |

| I-2  | BLOCK DIAGRAM                                 | B-I-2-1   |

| I-3  | LIST OF PINS                                  | B-I-3-1   |

|      | List of External I/O Pins                     | B-I-3-1   |

| II ( | CORE BLOCK                                    |           |

| II-1 | INTRODUCTION                                  | B-II-1-1  |

| II-2 | CPU AND OPERATING MODE                        | B-II-2-1  |

|      | CPU                                           | B-II-2-1  |

|      | Standby Mode                                  |           |

|      | HALT Mode                                     |           |

|      | SLEEP Mode                                    |           |

|      | Notes on Standby Mode                         |           |

|      | Test Mode                                     |           |

|      | Debug Mode                                    |           |

|      | Trap Table                                    |           |

| II-3 | INITIAL RESET                                 | B-II-3-1  |

|      | Pins for Initial Reset                        | B-II-3-1  |

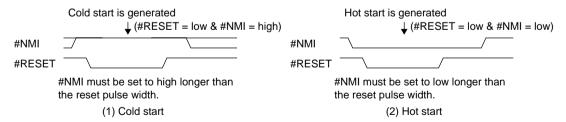

|      | Cold Start and Hot Start                      |           |

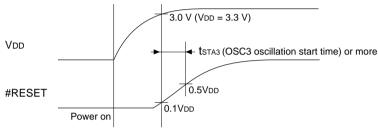

|      | Power-on Reset                                |           |

|      | Reset Pulse                                   |           |

|      | Boot Address                                  | B-II-3-3  |

|      | Notes Related to Initial Reset                | B-II-3-3  |

| II-4 | BCU (Bus Control Unit)                        | B-II-4-1  |

|      | Pin Assignment for External System Interface  | B-II-4-1  |

|      | I/O Pin List                                  | B-II-4-1  |

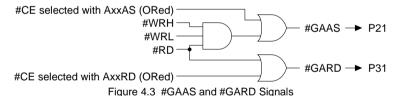

|      | Combination of System Bus Control Signals     | B-II-4-3  |

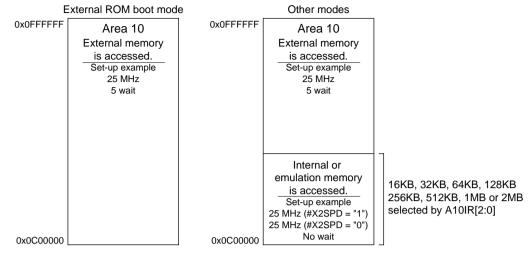

|      | Memory Area                                   | B-II-4-4  |

|      | Memory Map                                    | B-II-4-4  |

|      | External Memory Map and Chip Enable           | B-II-4-5  |

|      | Using Internal Memory on External Memory Area | B-II-4-7  |

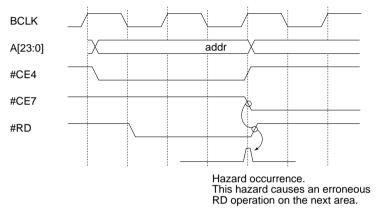

|      | Exclusive Signals for Areas                   | B-II-4-7  |

|      | Area 10                                       | B-II-4-8  |

|      | Area 3                                        | B-II-4-9  |

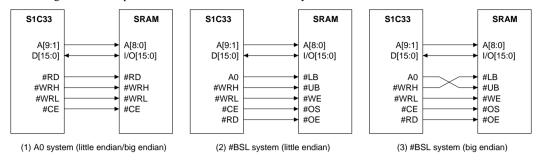

|      | Setting External Bus Conditions               | B-II-4-10 |

|      | Setting Device Type and Size                  |           |

|      | Setting SRAM Timing Conditions                | B-II-4-11 |

|      | Setting Timing Conditions of Burst ROM        | B-II-4-12 |

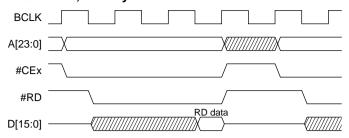

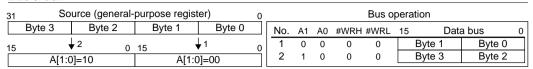

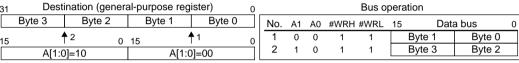

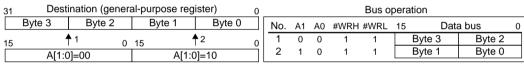

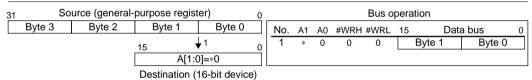

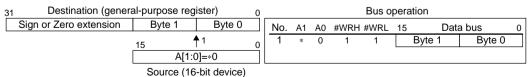

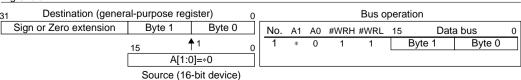

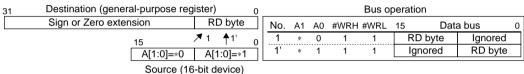

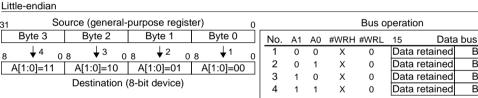

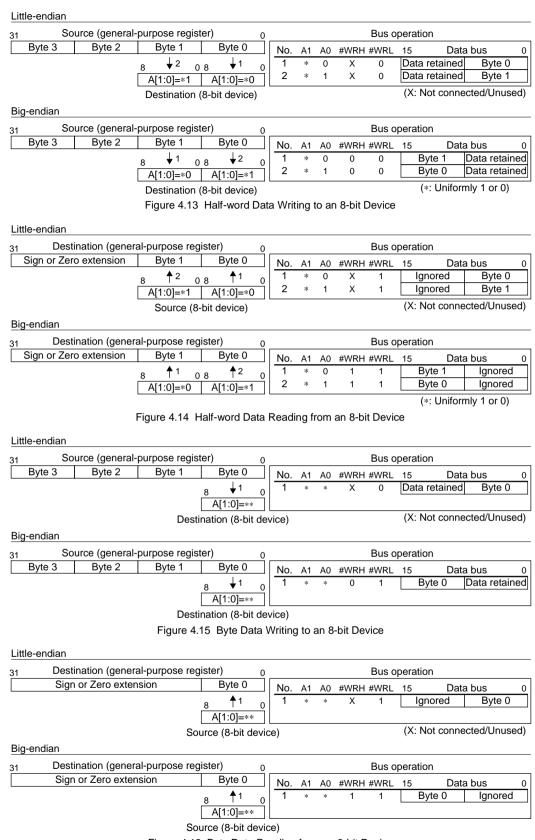

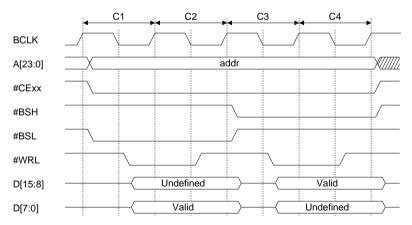

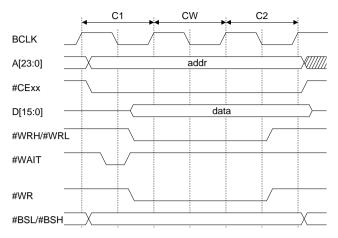

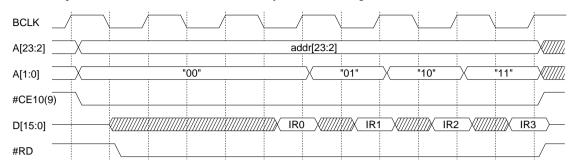

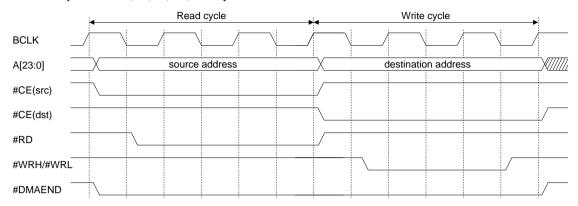

|      | Bus Operation                                 | B-II-4-13 |

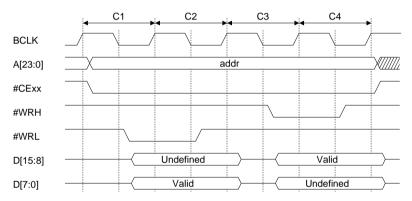

|      | Data Arrangement in Memory                    | B-II-4-13 |

|      | Bus Operation of External Memory              | B-II-4-13 |

## TABLE OF CONTENTS

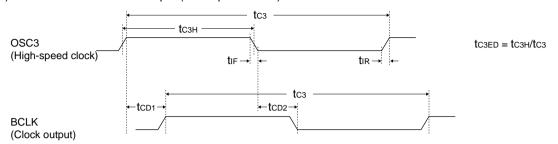

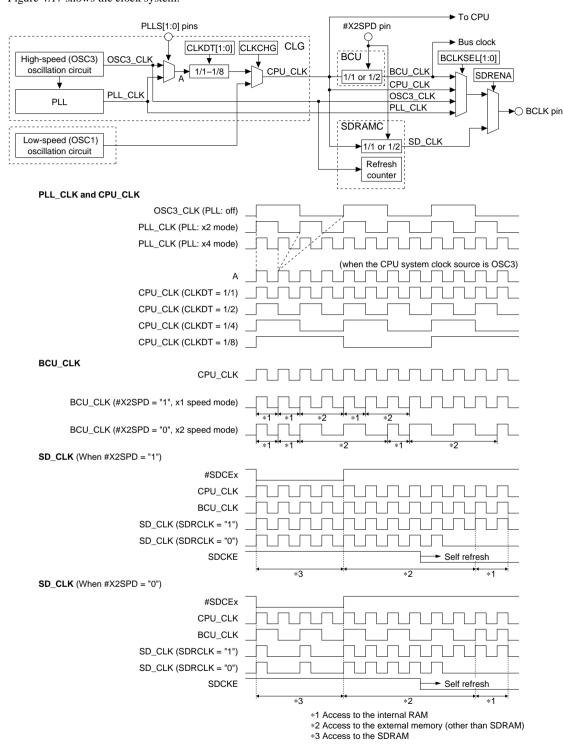

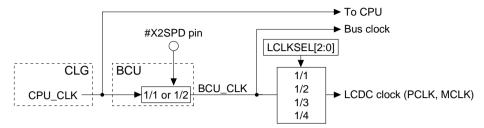

|      | Bus Clock                                           | B-II-4-17 |

|------|-----------------------------------------------------|-----------|

|      | Bus Speed Mode                                      | B-II-4-18 |

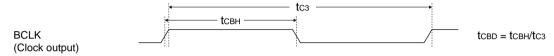

|      | Bus Clock Output                                    | B-II-4-18 |

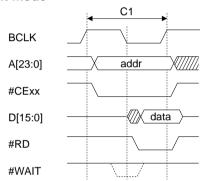

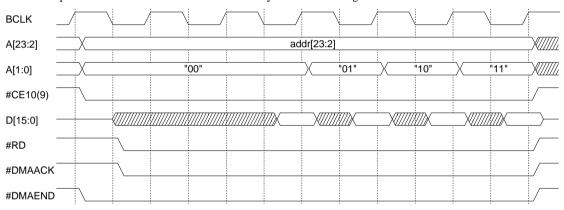

|      | Bus Cycles in External System Interface             | B-II-4-19 |

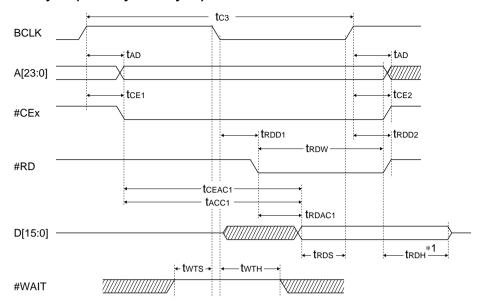

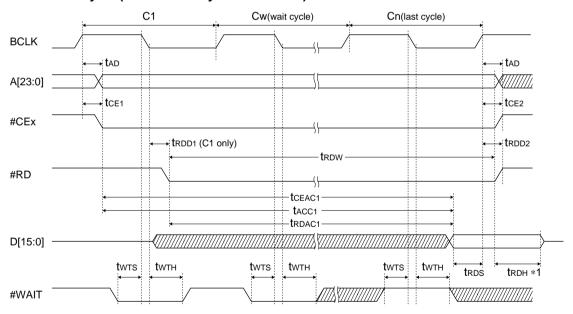

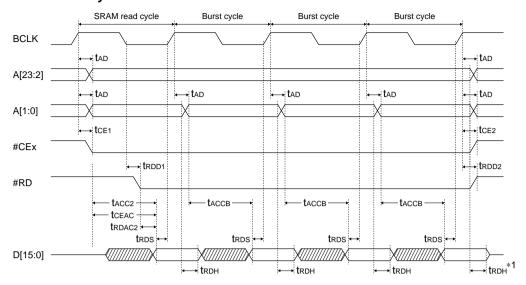

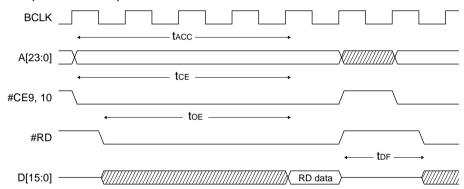

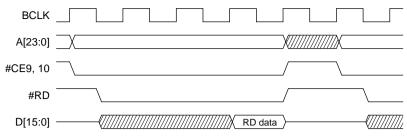

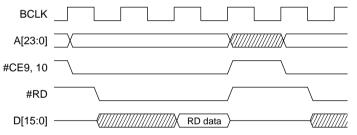

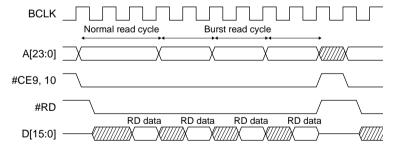

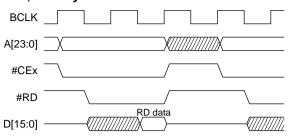

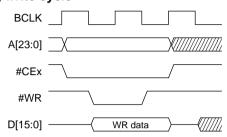

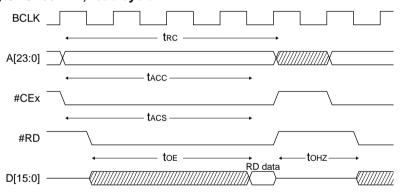

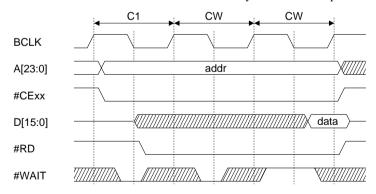

|      | SRAM Read Cycles                                    |           |

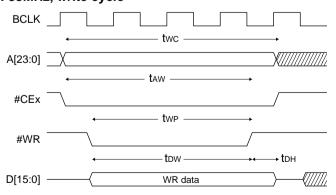

|      | Bus Timing                                          | B-II-4-20 |

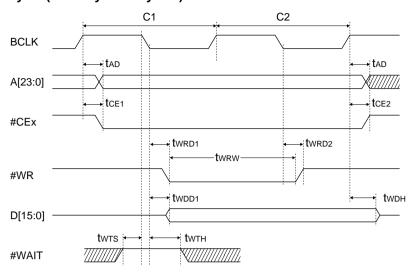

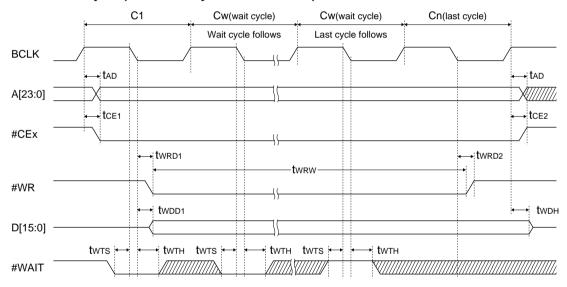

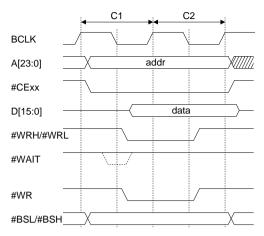

|      | SRAM Write Cycles                                   |           |

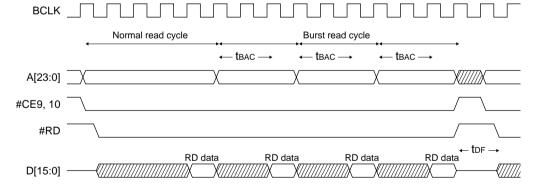

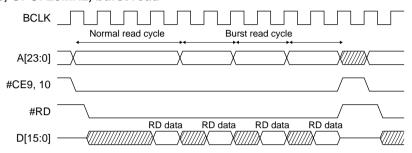

|      | Burst ROM Read Cycles                               |           |

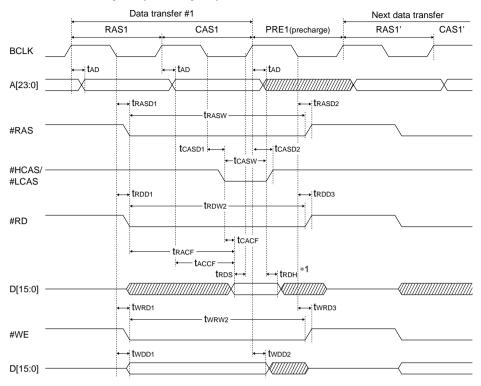

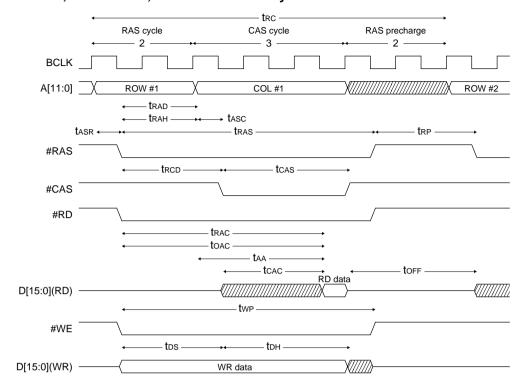

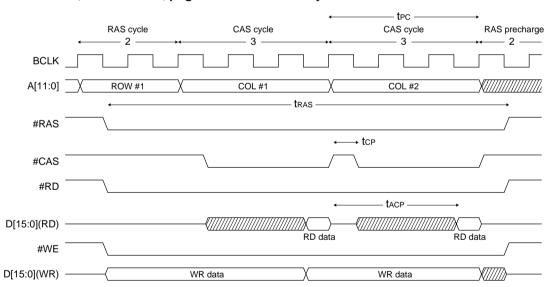

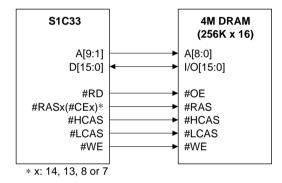

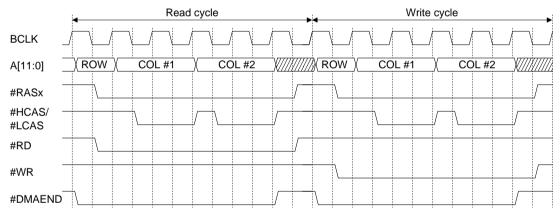

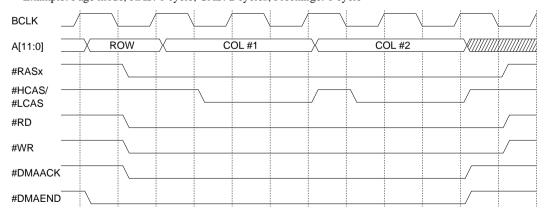

|      | DRAM Direct Interface                               |           |

|      | Outline of DRAM Interface                           |           |

|      | DRAM Setting Conditions                             |           |

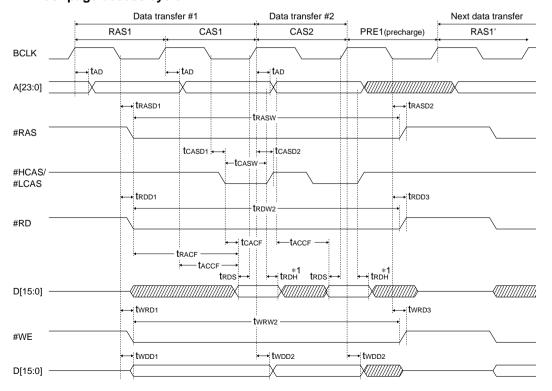

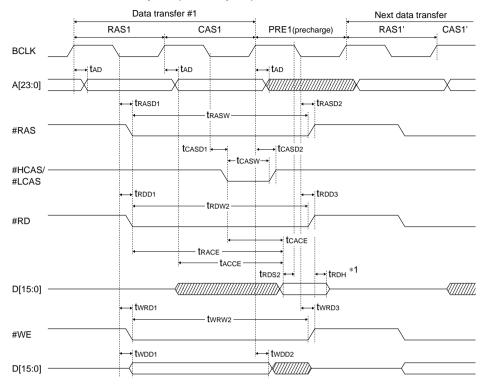

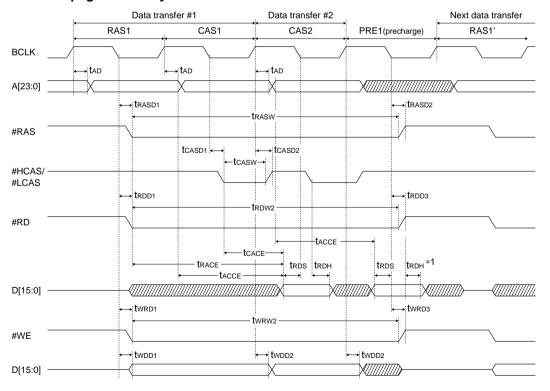

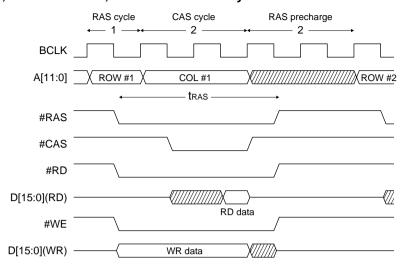

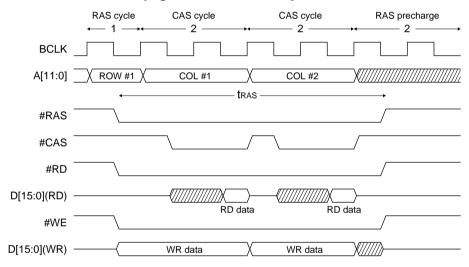

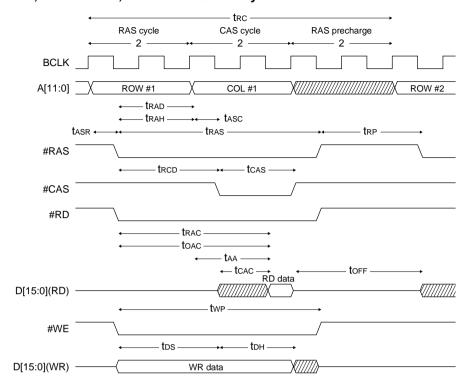

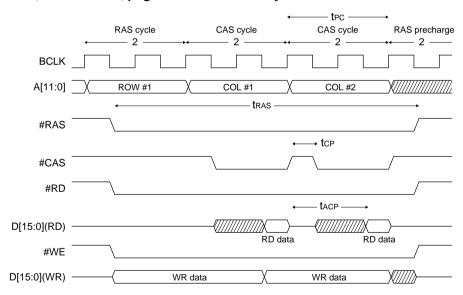

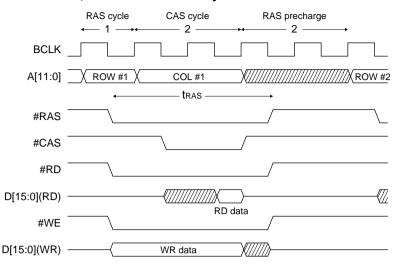

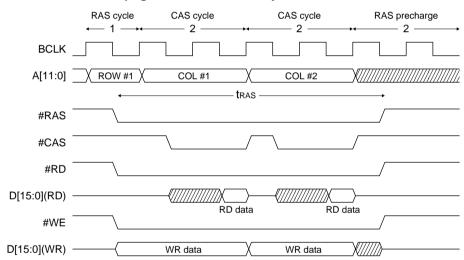

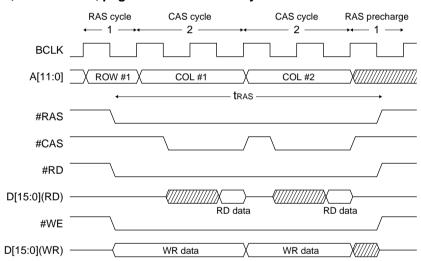

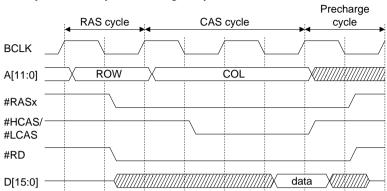

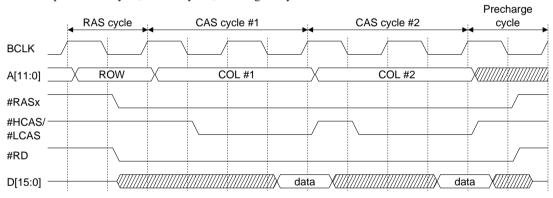

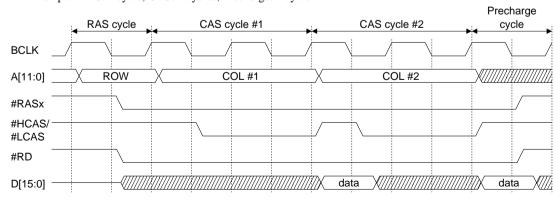

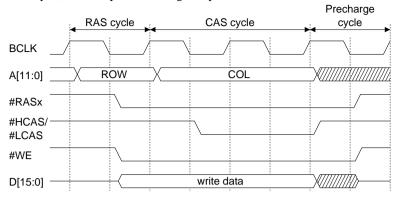

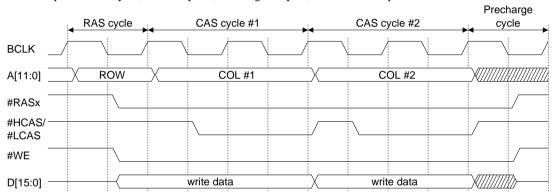

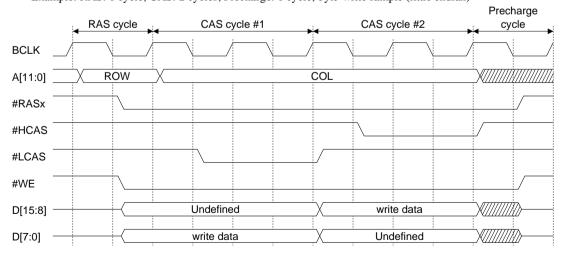

|      | DRAM Read/Write Cycles                              |           |

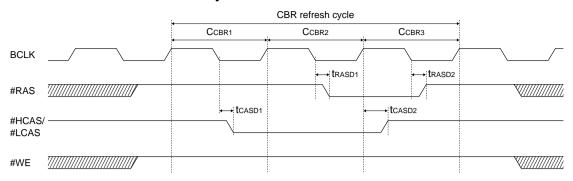

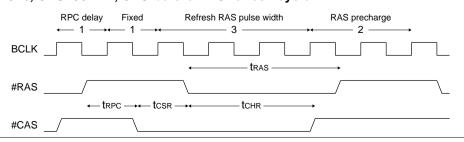

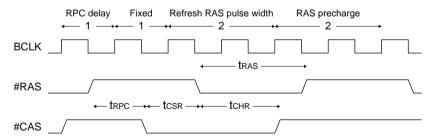

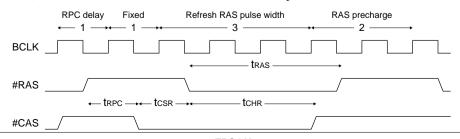

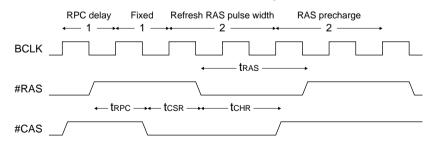

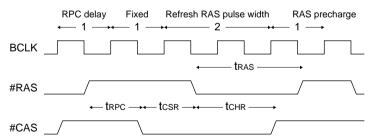

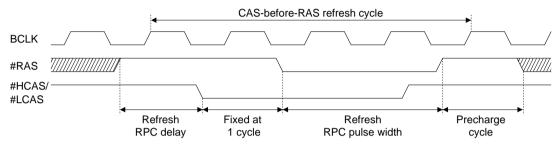

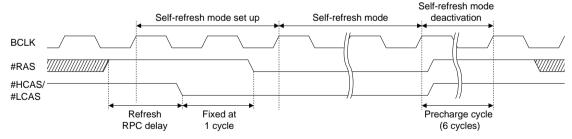

|      | DRAM Refresh Cycles                                 |           |

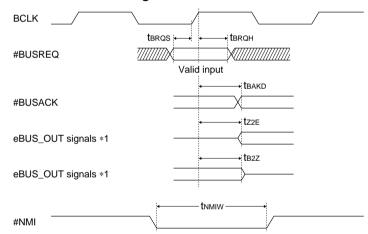

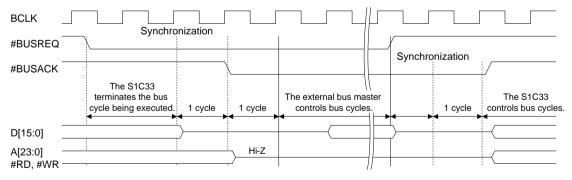

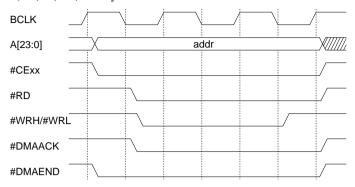

|      | Releasing External Bus                              |           |

|      | Power-down Control by External Device               |           |

|      | I/O Memory of BCU                                   |           |

|      | · · · · · · · · · · · · · · · · · · ·               |           |

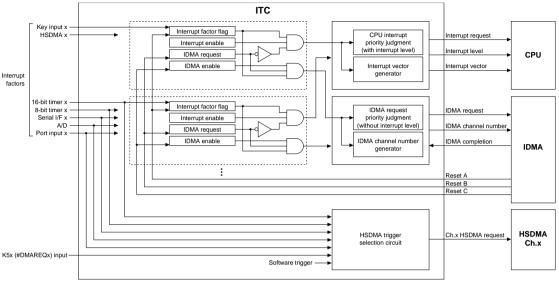

| II-5 | ITC (Interrupt Controller)                          |           |

|      | Outline of Interrupt Functions                      | B-II-5-1  |

|      | Maskable Interrupts                                 |           |

|      | Interrupt Factors and Intelligent DMA               | B-II-5-3  |

|      | Nonmaskable Interrupt (NMI)                         | B-II-5-3  |

|      | Interrupt Processing by the CPU                     | B-II-5-3  |

|      | Clearing Standby Mode by Interrupts                 | B-II-5-3  |

|      | Trap Table                                          | B-II-5-4  |

|      | Control of Maskable Interrupts                      | B-II-5-5  |

|      | Structure of the Interrupt Controller               | B-II-5-5  |

|      | Processor Status Register (PSR)                     | B-II-5-5  |

|      | Interrupt Factor Flag and Interrupt Enable Register | B-II-5-6  |

|      | Interrupt Priority Register and Interrupt Levels    |           |

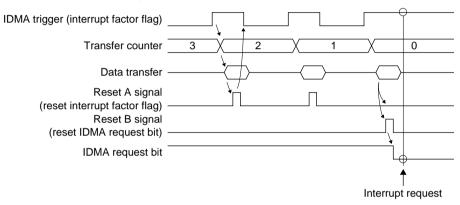

|      | IDMA Invocation                                     | B-II-5-9  |

|      | HSDMA Invocation                                    | B-II-5-11 |

|      | I/O Memory of Interrupt Controller                  | B-II-5-12 |

|      | Programming Notes                                   | B-II-5-25 |

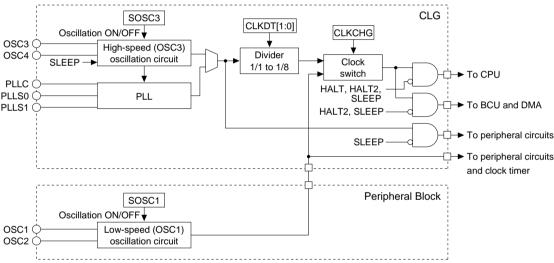

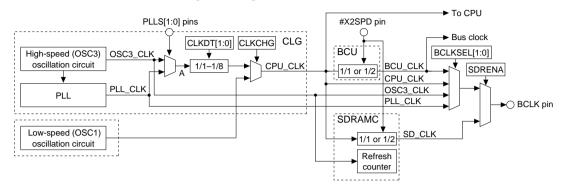

| II-6 | CLG (Clock Generator)                               | B-II-6-1  |

|      | Configuration of Clock Generator                    | B-II-6-1  |

|      | I/O Pins of Clock Generator                         | B-II-6-2  |

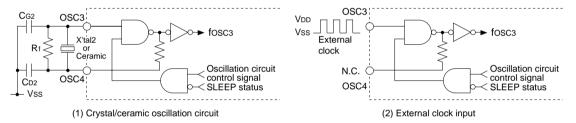

|      | High-Speed (OSC3) Oscillation Circuit               | B-II-6-2  |

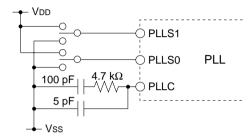

|      | PLL                                                 | B-II-6-3  |

|      | Controlling Oscillation                             | B-II-6-3  |

|      | Setting and Switching Over the CPU Operating Clock  | B-II-6-4  |

|      | Power-Control Register Protection Flag              |           |

|      | Operation in Standby Mode                           |           |

|      | I/O Memory of Clock Generator                       |           |

|      | Programming Notes                                   |           |

| II-7 |                                                     |           |

|      | Debug Circuit                                       | B-II-7-1  |

|      | I/O Pins of Dahua Circuit                           | R-II-7-1  |

## **III PERIPHERAL BLOCK**

| III-1 | INTRODUCTION                                              | B-III-1-1  |

|-------|-----------------------------------------------------------|------------|

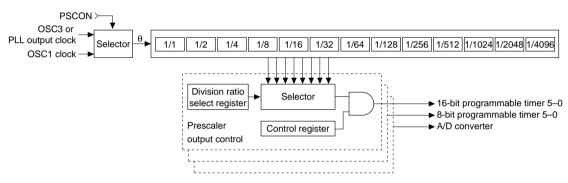

| III-2 | PRESCALER                                                 | B-III-2-1  |

|       | Configuration of Prescaler                                | B-III-2-1  |

|       | Source Clock                                              |            |

|       | Selecting Division Ratio and Output Control for Prescaler | B-III-2-2  |

|       | Source Clock Output to 8-Bit Programmable Timer           |            |

|       | I/O Memory of Prescaler                                   | B-III-2-3  |

|       | Programming Notes                                         | B-III-2-8  |

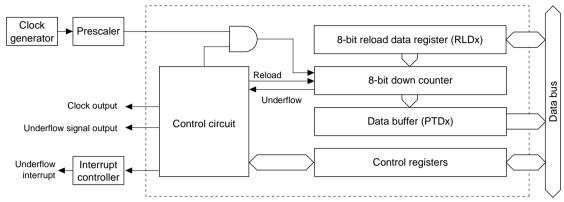

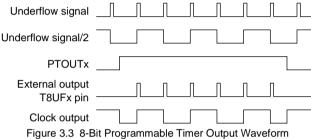

| III-3 | 8-BIT PROGRAMMABLE TIMERS                                 | B-III-3-1  |

|       | Configuration of 8-Bit Programmable Timer                 | B-III-3-1  |

|       | Output Pins of 8-Bit Programmable Timers                  |            |

|       | Uses of 8-Bit Programmable Timers                         |            |

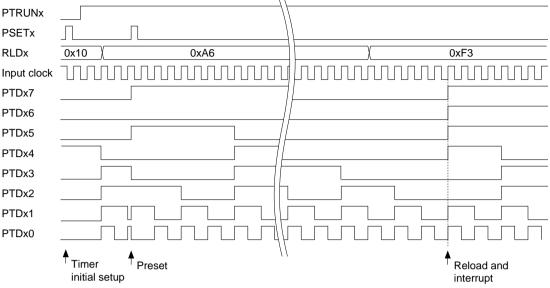

|       | Control and Operation of 8-Bit Programmable Timer         | B-III-3-4  |

|       | Control of Clock Output                                   | B-III-3-7  |

|       | 8-Bit Programmable Timer Interrupts and DMA               |            |

|       | I/O Memory of 8-Bit Programmable Timers                   | B-III-3-10 |

|       | Programming Notes                                         | B-III-3-17 |

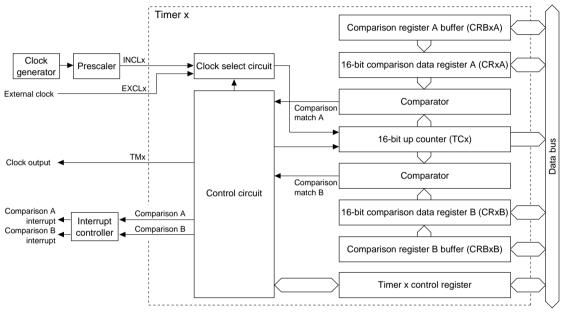

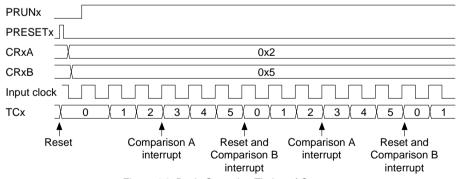

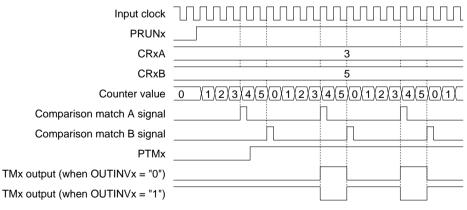

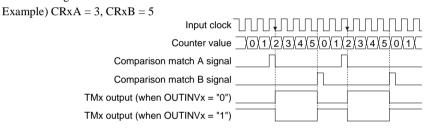

| III-4 | 16-BIT PROGRAMMABLE TIMERS                                | B-III-4-1  |

|       | Configuration of 16-Bit Programmable Timer                | B-III-4-1  |

|       | I/O Pins of 16-Bit Programmable Timers                    |            |

|       | Uses of 16-Bit Programmable Timers                        |            |

|       | Control and Operation of 16-Bit Programmable Timer        |            |

|       | Controlling Clock Output                                  | B-III-4-7  |

|       | 16-Bit Programmable Timer Interrupts and DMA              | B-III-4-9  |

|       | I/O Memory of 16-Bit Programmable Timers                  | B-III-4-12 |

|       | Programming Notes                                         | B-III-4-25 |

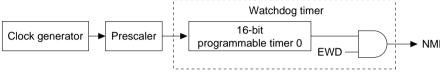

| III-5 | WATCHDOG TIMER                                            | B-III-5-1  |

|       | Configuration of Watchdog Timer                           | B-III-5-1  |

|       | Control of Watchdog Timer                                 |            |

|       | Operation in Standby Modes                                |            |

|       | I/O Memory of Watchdog Timer                              |            |

|       | Programming Notes                                         |            |

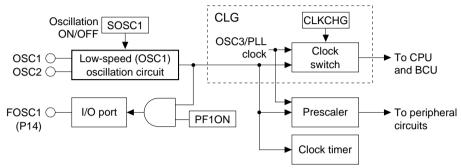

| III-6 | LOW-SPEED (OSC1) OSCILLATION CIRCUIT                      |            |

|       | Configuration of Low-Speed (OSC1) Oscillation Circuit     |            |

|       | I/O Pins of Low-Speed (OSC1) Oscillation Circuit          |            |

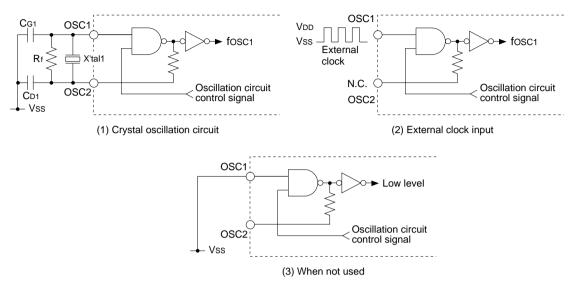

|       | Oscillator Types                                          |            |

|       | Controlling Oscillation                                   |            |

|       | Switching Over the CPU Operating Clock                    |            |

|       | Power-Control Register Protection Flag                    |            |

|       | Operation in Standby Mode                                 |            |

|       | OSC1 Clock Output to External Devices                     |            |

|       | I/O Memory of Low-Speed (OSC1) Oscillation Circuit        |            |

|       | Programming Notes                                         | B-III-6-8  |

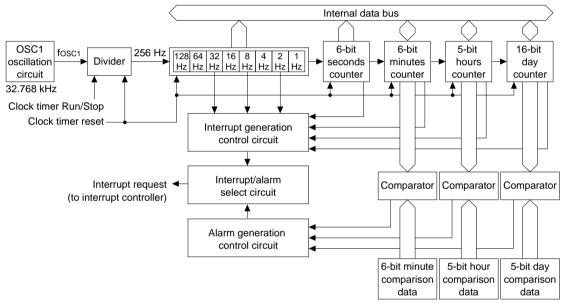

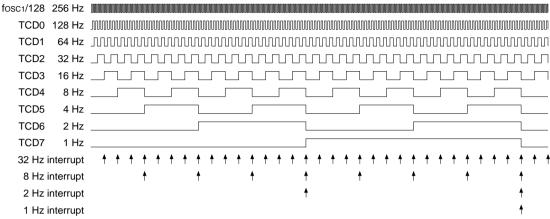

| III-7 | CLOCK TIMER                                          | B-III-7-1  |

|-------|------------------------------------------------------|------------|

|       | Configuration of Clock Timer                         | B-III-7-1  |

|       | Control and Operation of the Clock Timer             |            |

|       | Interrupt Function                                   | B-III-7-4  |

|       | Examples of Use of Clock Timer                       | B-III-7-6  |

|       | I/O Memory of Clock Timer                            | B-III-7-7  |

|       | Programming Notes                                    | B-III-7-12 |

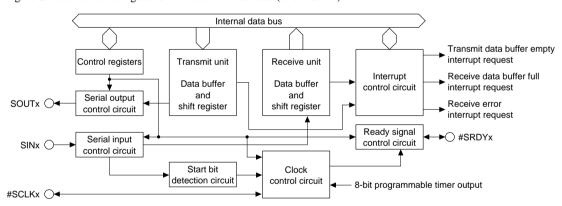

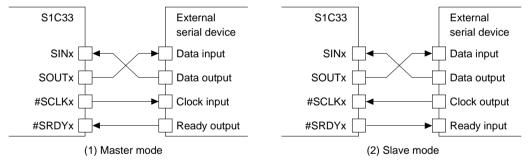

| III-8 | SERIAL INTERFACE                                     | B-III-8-1  |

|       | Configuration of Serial Interfaces                   | B-III-8-1  |

|       | Features of Serial Interfaces                        | B-III-8-1  |

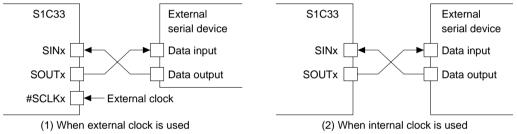

|       | I/O Pins of Serial Interface                         | B-III-8-2  |

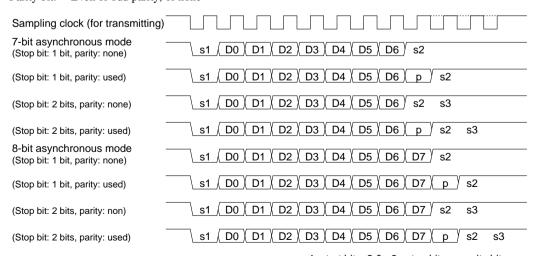

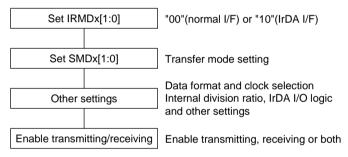

|       | Setting Transfer Mode                                | B-III-8-3  |

|       | Clock-Synchronized Interface                         | B-III-8-4  |

|       | Outline of Clock-Synchronized Interface              | B-III-8-4  |

|       | Setting Clock-Synchronized Interface                 | B-III-8-5  |

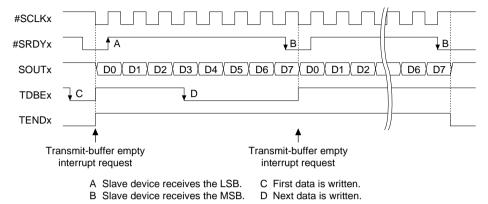

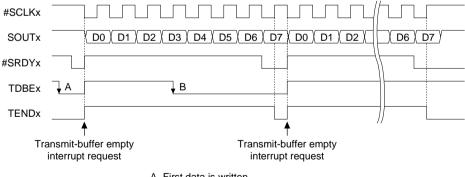

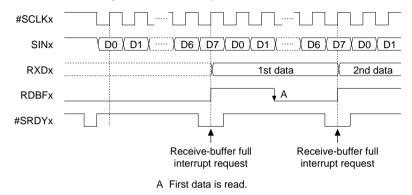

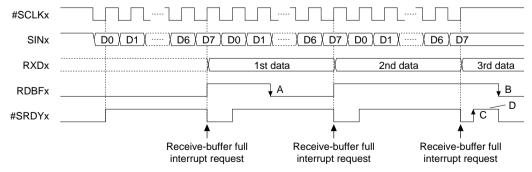

|       | Control and Operation of Clock-Synchronized Transfer |            |

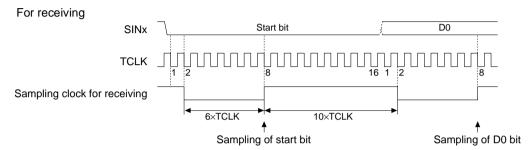

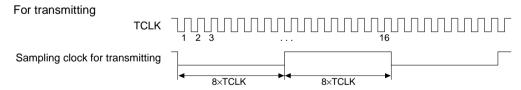

|       | Asynchronous Interface                               |            |

|       | Outline of Asynchronous Interface                    |            |

|       | Setting Asynchronous Interface                       |            |

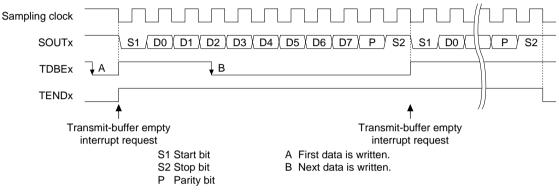

|       | Control and Operation of Asynchronous Transfer       |            |

|       | IrDA Interface                                       |            |

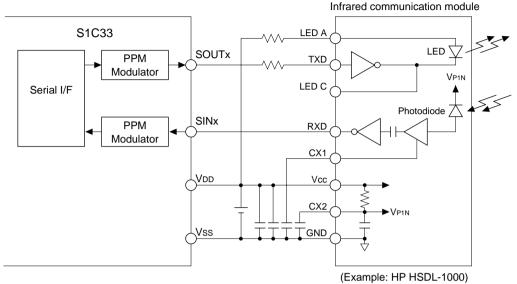

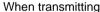

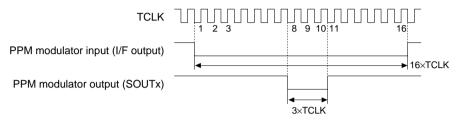

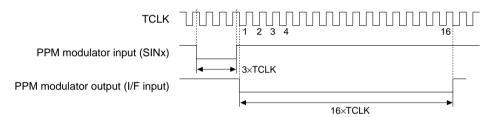

|       | Outline of IrDA Interface                            | B-III-8-21 |

|       | Setting IrDA Interface                               | B-III-8-21 |

|       | Control and Operation of IrDA Interface              | B-III-8-23 |

|       | Serial Interface Interrupts and DMA                  |            |

|       | I/O Memory of Serial Interface                       | B-III-8-28 |

|       | Programming Notes                                    | B-III-8-46 |

| III-9 | INPUT/OUTPUT PORTS                                   | B-III-9-1  |

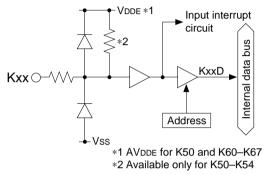

|       | Input Ports (K Ports)                                | B-III-9-1  |

|       | Structure of Input Port                              | B-III-9-1  |

|       | Input-Port Pins                                      | B-III-9-2  |

|       | Notes on Use                                         | B-III-9-2  |

|       | I/O Memory of Input Ports                            | B-III-9-3  |

|       | I/O Ports (P Ports)                                  | B-III-9-4  |

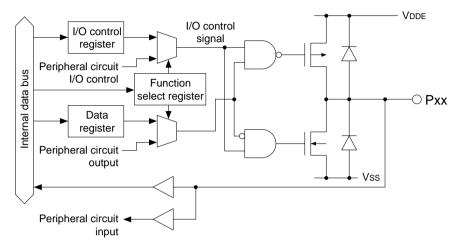

|       | Structure of I/O Port                                | B-III-9-4  |

|       | I/O Port Pins                                        | B-III-9-4  |

|       | I/O Control Register and I/O Modes                   | B-III-9-5  |

|       | I/O Memory of I/O Ports                              | B-III-9-6  |

|       | Input Interrupt                                      | B-III-9-12 |

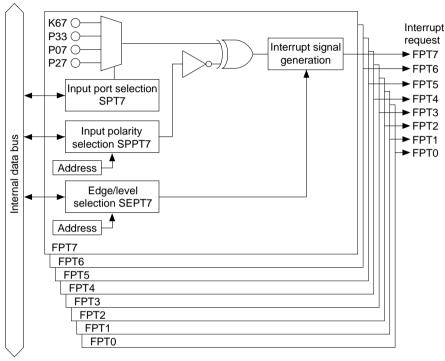

|       | Port Input Interrupt                                 | B-III-9-12 |

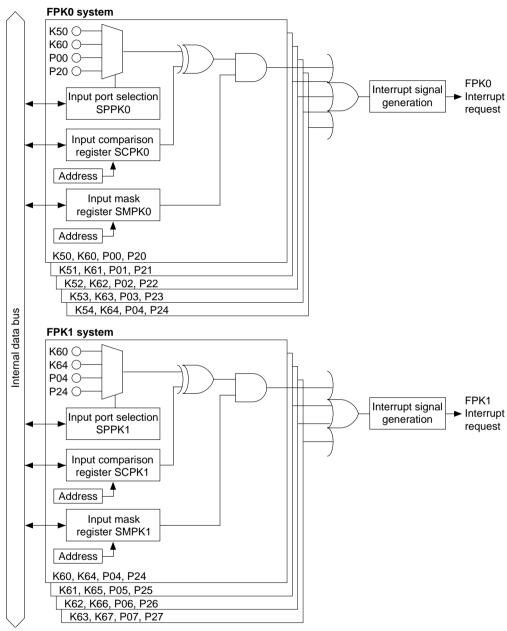

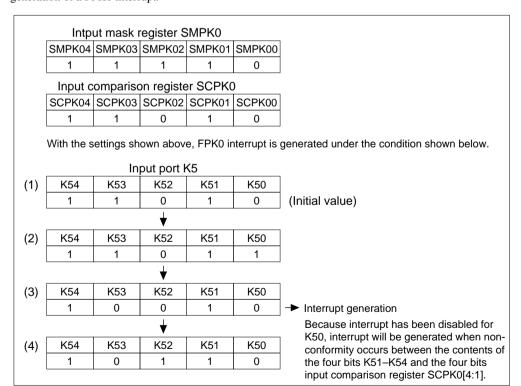

|       | Key Input Interrupt                                  |            |

|       | Control Registers of the Interrupt Controller        |            |

|       | I/O Memory for Input Interrupts                      |            |

|       | Programming Notes                                    | B-III-9-25 |

## IV ANALOG BLOCK

| IV-1 | INTRODUCTION                                 | B-IV-1-1  |

|------|----------------------------------------------|-----------|

| IV-2 | A/D CONVERTER                                | B-IV-2-1  |

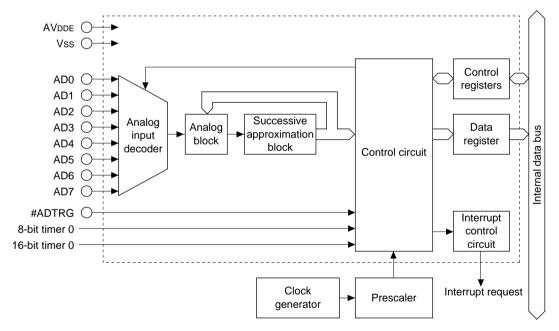

|      | Features and Structure of A/D Converter      | B-IV-2-1  |

|      | I/O Pins of A/D Converter                    | B-IV-2-2  |

|      | Setting A/D Converter                        | B-IV-2-3  |

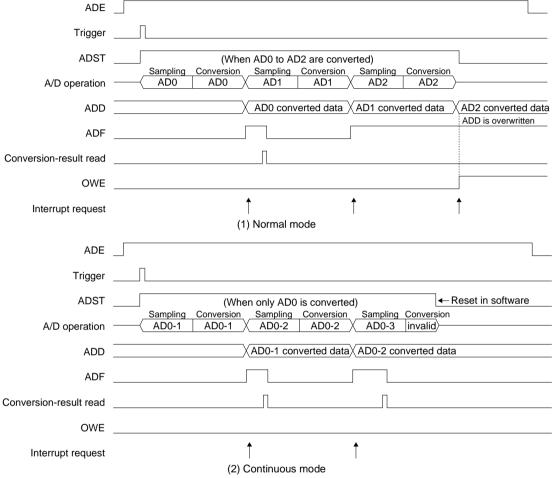

|      | Control and Operation of A/D Conversion      | B-IV-2-5  |

|      | A/D Converter Interrupt and DMA              |           |

|      | I/O Memory of A/D Converter                  | B-IV-2-9  |

|      | Programming Notes                            | B-IV-2-15 |

| V D  | DMA BLOCK                                    |           |

| V-1  | INTRODUCTION                                 | B-V-1-1   |

| V-2  | HSDMA (High-Speed DMA)                       | B-V-2-1   |

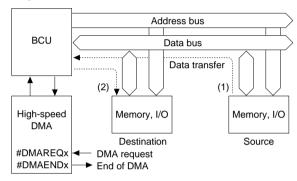

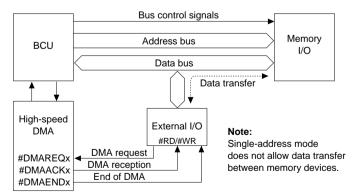

|      | Functional Outline of HSDMA                  |           |

|      | I/O Pins of HSDMA                            |           |

|      | Programming Control Information              | B-V-2-3   |

|      | Setting the Registers in Dual-Address Mode   | B-V-2-3   |

|      | Setting the Registers in Single-Address Mode | B-V-2-6   |

|      | Enabling/Disabling DMA Transfer              | B-V-2-7   |

|      | Trigger Factor                               | B-V-2-8   |

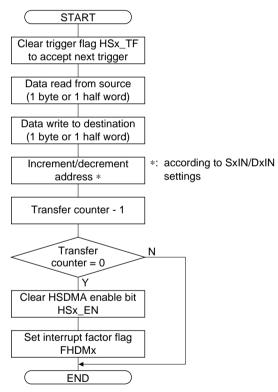

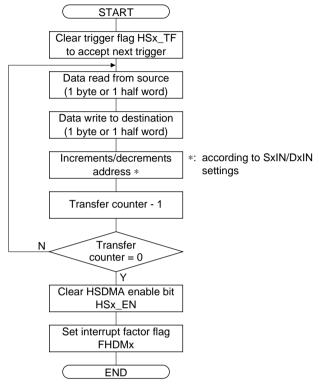

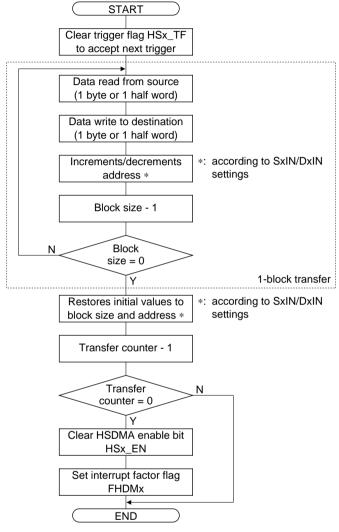

|      | Operation of HSDMA                           | B-V-2-9   |

|      | Operation in Dual-Address Mode               | B-V-2-9   |

|      | Operation in Single-Address Mode             | B-V-2-12  |

|      | Timing Chart                                 | B-V-2-13  |

|      | Interrupt Function of HSDMA                  | B-V-2-15  |

|      | I/O Memory of HSDMA                          | B-V-2-17  |

|      | Programming Notes                            | B-V-2-36  |

| V-3  | IDMA (Intelligent DMA)                       | B-V-3-1   |

|      | Functional Outline of IDMA                   | B-V-3-1   |

|      | Programming Control Information              | B-V-3-1   |

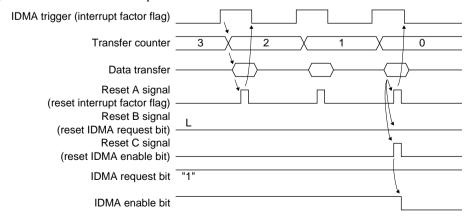

|      | IDMA Invocation                              | B-V-3-5   |

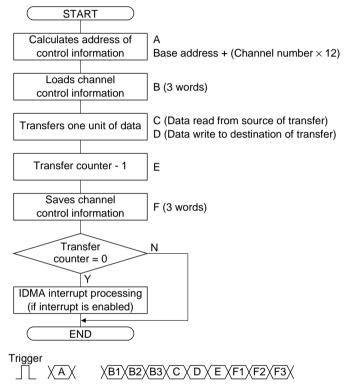

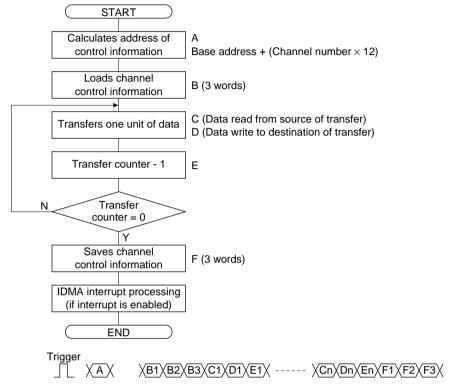

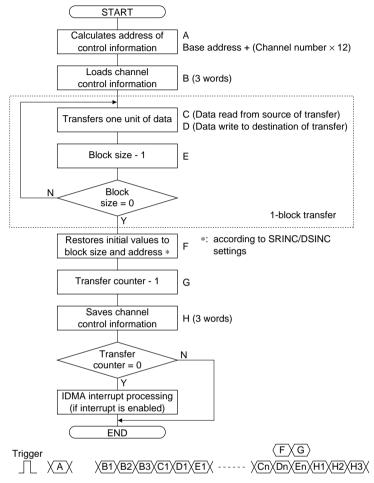

|      | Operation of IDMA                            | B-V-3-8   |

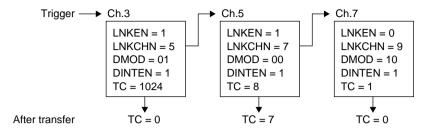

|      | Linking                                      | B-V-3-12  |

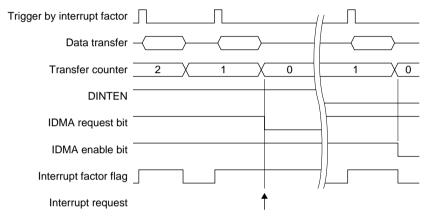

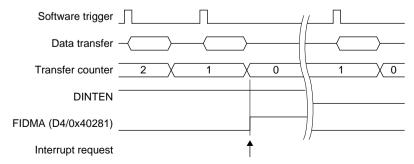

|      | Interrupt Function of Intelligent DMA        | B-V-3-13  |

|      | I/O Memory of Intelligent DMA                | B-V-3-14  |

|      | Programming Notes                            | B-V-3-17  |

|      |                                              |           |

## VI SDRAM CONTROLLER BLOCK

| VI-1  | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                         | B-VI-1-1                                                                                                                                                                                                                         |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VI-2  | SDRAM INTERFACE                                                                                                                                                                                                                                                                                                                                                      | B-VI-2-1                                                                                                                                                                                                                         |

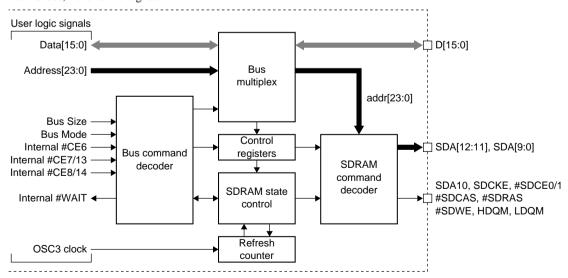

|       | Outline of SDRAM Interface                                                                                                                                                                                                                                                                                                                                           | B-VI-2-1                                                                                                                                                                                                                         |

|       | SDRAM Controller Block Diagram                                                                                                                                                                                                                                                                                                                                       | B-VI-2-1                                                                                                                                                                                                                         |

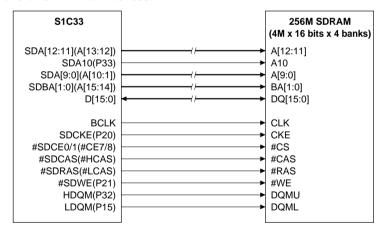

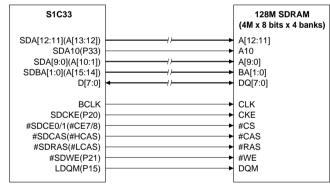

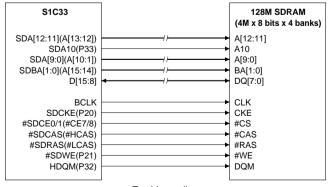

|       | I/O Pins and Connection                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                  |

|       | I/O Pins                                                                                                                                                                                                                                                                                                                                                             | B-VI-2-2                                                                                                                                                                                                                         |

|       | Connection Examples                                                                                                                                                                                                                                                                                                                                                  | B-VI-2-2                                                                                                                                                                                                                         |

|       | SDRAM Controller Configuration                                                                                                                                                                                                                                                                                                                                       | B-VI-2-5                                                                                                                                                                                                                         |

|       | Setting PLL                                                                                                                                                                                                                                                                                                                                                          | B-VI-2-5                                                                                                                                                                                                                         |

|       | BCU Configuration                                                                                                                                                                                                                                                                                                                                                    | B-VI-2-5                                                                                                                                                                                                                         |

|       | SDRAM Setting Conditions                                                                                                                                                                                                                                                                                                                                             | B-VI-2-6                                                                                                                                                                                                                         |

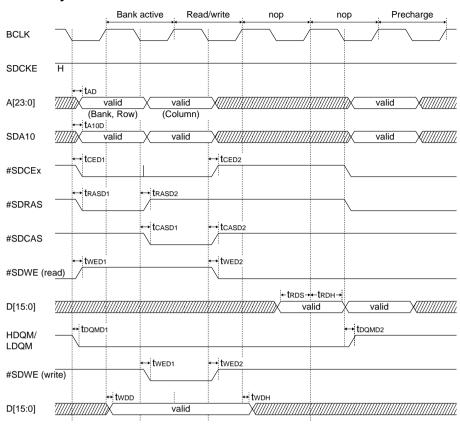

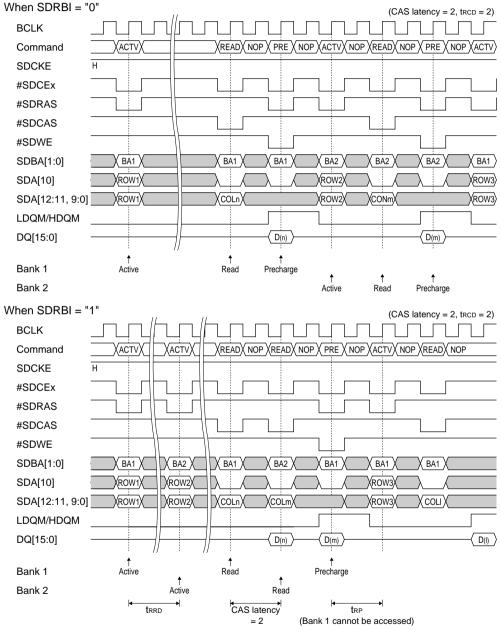

|       | SDRAM Operation                                                                                                                                                                                                                                                                                                                                                      | B-VI-2-12                                                                                                                                                                                                                        |

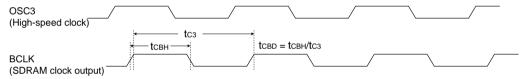

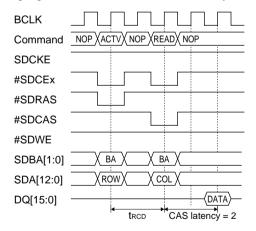

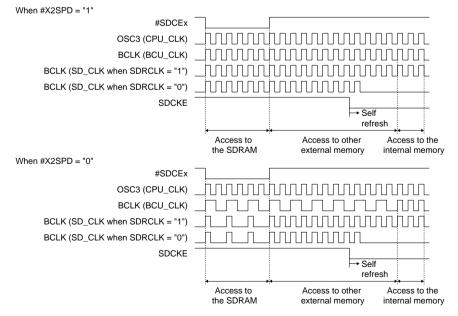

|       | Synchronous Clock                                                                                                                                                                                                                                                                                                                                                    | B-VI-2-12                                                                                                                                                                                                                        |

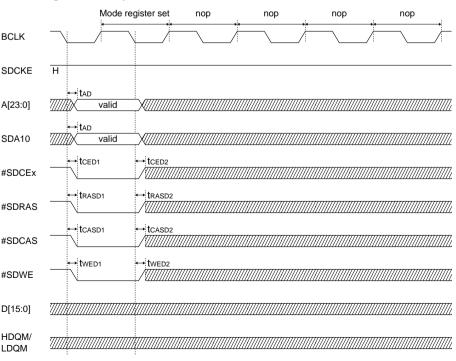

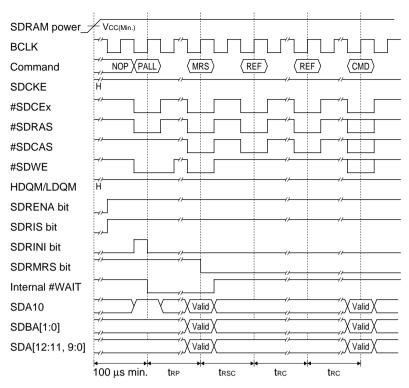

|       | Power-up and Initialization                                                                                                                                                                                                                                                                                                                                          | B-VI-2-13                                                                                                                                                                                                                        |

|       | SDRAM Commands                                                                                                                                                                                                                                                                                                                                                       | B-VI-2-14                                                                                                                                                                                                                        |

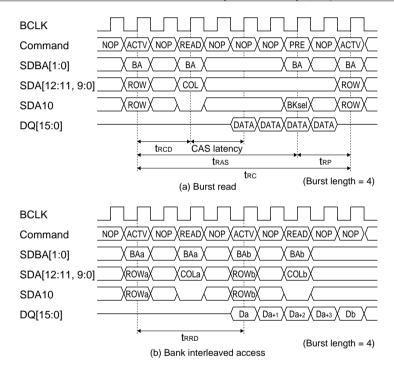

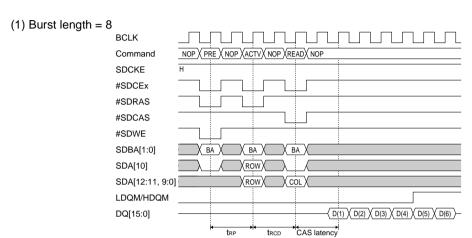

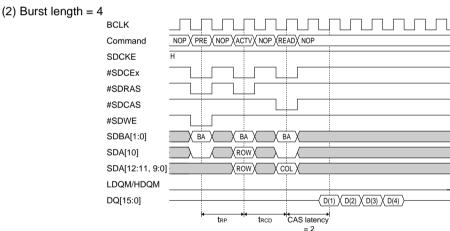

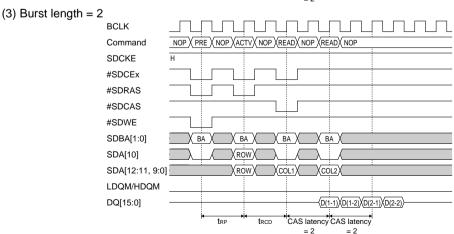

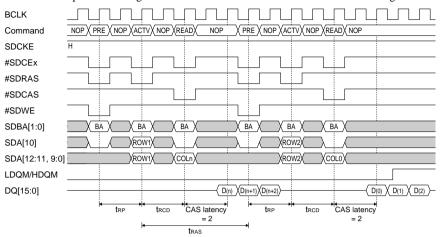

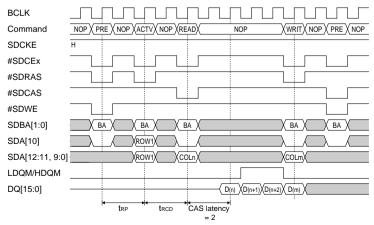

|       | Burst Read Cycle                                                                                                                                                                                                                                                                                                                                                     | B-VI-2-15                                                                                                                                                                                                                        |

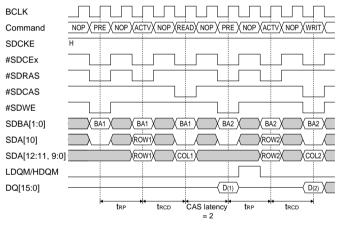

|       | Single Read/Single Write                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                  |

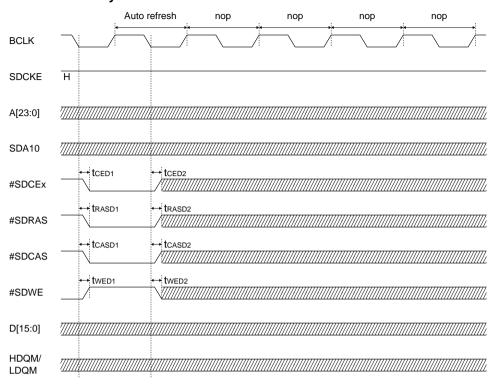

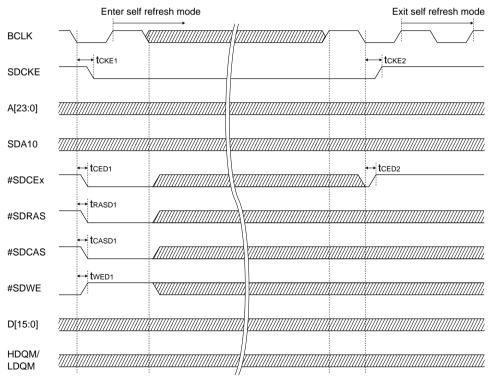

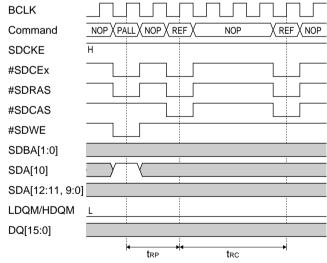

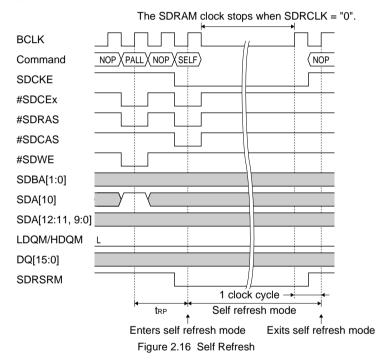

|       | Refresh Mode                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                  |

|       | Power-down Mode                                                                                                                                                                                                                                                                                                                                                      | B-VI-2-19                                                                                                                                                                                                                        |

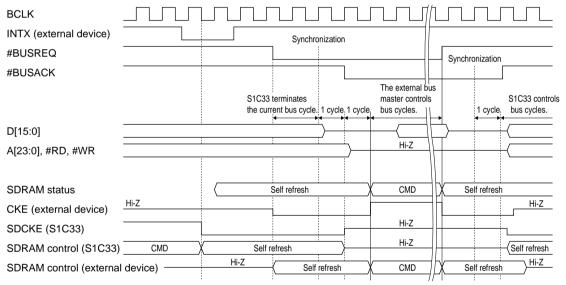

|       | Bus Release Procedure                                                                                                                                                                                                                                                                                                                                                | B-VI-2-19                                                                                                                                                                                                                        |

|       | I/O Memory of SDRAM Interface                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                  |

|       | Programming Notes                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                  |

| VII L | Examples of SDRAM Controller Initialization Program                                                                                                                                                                                                                                                                                                                  | B-VI-2-33                                                                                                                                                                                                                        |

|       | Examples of SDRAM Controller Initialization Program                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                  |

| VII-1 | Examples of SDRAM Controller Initialization Program                                                                                                                                                                                                                                                                                                                  | B-VII-1-1                                                                                                                                                                                                                        |

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                              | B-VII-1-1                                                                                                                                                                                                                        |

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                              | B-VII-1-1B-VII-2-1                                                                                                                                                                                                               |

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                              | B-VII-1-1B-VII-2-1B-VII-2-1                                                                                                                                                                                                      |

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION  LCD CONTROLLER  Overview  Features                                                                                                                                                                                                                                          | B-VII-1-1B-VII-2-1B-VII-2-1B-VII-2-1B-VII-2-1                                                                                                                                                                                    |

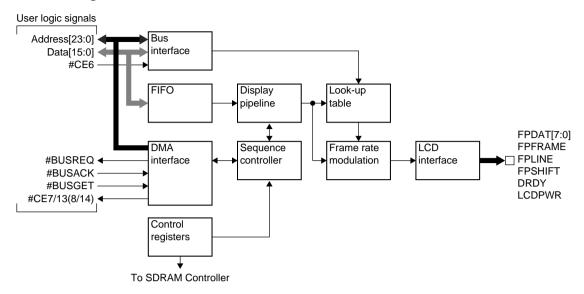

| VII-1 | Examples of SDRAM Controller Initialization Program  CD CONTROLLER BLOCK  INTRODUCTION  LCD CONTROLLER  Overview  Features  Block Diagram                                                                                                                                                                                                                            | B-VII-1-1B-VII-2-1B-VII-2-1B-VII-2-1B-VII-2-3B-VII-2-4                                                                                                                                                                           |

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                              | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-4  B-VII-2-5                                                                                                                                                                 |

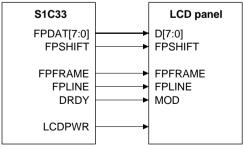

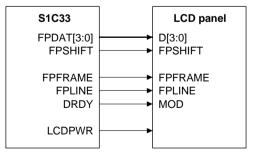

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION  LCD CONTROLLER  Overview                                                                                                                                                                                                                                                    | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-4  B-VII-2-5  B-VII-2-5                                                                                                                                                      |

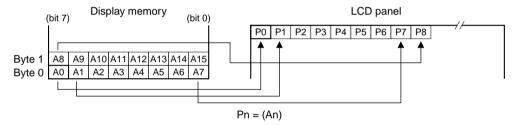

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION  LCD CONTROLLER  Overview                                                                                                                                                                                                                                                    | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-4  B-VII-2-5  B-VII-2-5  B-VII-2-5                                                                                                                                |

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION  LCD CONTROLLER  Overview                                                                                                                                                                                                                                                    | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-4  B-VII-2-5  B-VII-2-5  B-VII-2-5  B-VII-2-5                                                                                                                     |

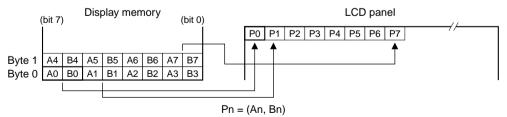

| VII-1 | Examples of SDRAM Controller Initialization Program  CD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                               | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-4  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-7                                                                                                                     |

| VII-1 | Examples of SDRAM Controller Initialization Program  CD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                               | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-3  B-VII-2-5  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-7  B-VII-2-8                                                                                                          |

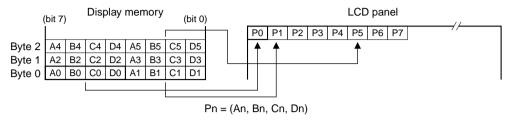

| VII-1 | Examples of SDRAM Controller Initialization Program  CD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                               | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-3  B-VII-2-5  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-7  B-VII-2-8  B-VII-2-8                                                                                               |

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                              | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-3  B-VII-2-5  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-8  B-VII-2-8  B-VII-2-8                                                                                    |

| VII-1 | Examples of SDRAM Controller Initialization Program                                                                                                                                                                                                                                                                                                                  | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-4  B-VII-2-5  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-7  B-VII-2-8  B-VII-2-8  B-VII-2-8  B-VII-2-8                                                              |

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                              | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-4  B-VII-2-5  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-7  B-VII-2-8  B-VII-2-8  B-VII-2-9  B-VII-2-9  B-VII-2-9                                                   |

| VII-1 | Examples of SDRAM Controller Initialization Program                                                                                                                                                                                                                                                                                                                  | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-3  B-VII-2-5  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-7  B-VII-2-7  B-VII-2-8  B-VII-2-8  B-VII-2-9  B-VII-2-11                                                  |

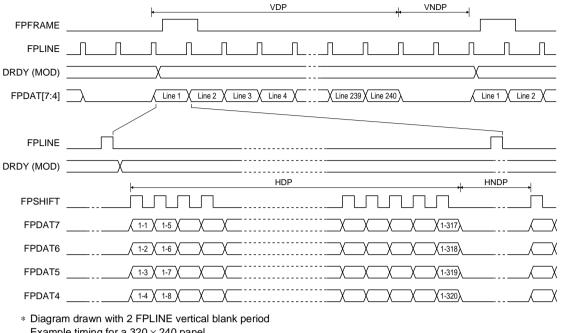

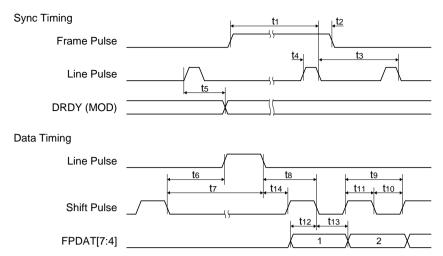

| VII-1 | Examples of SDRAM Controller Initialization Program  CD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                               | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-3  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-8  B-VII-2-8  B-VII-2-9  B-VII-2-9  B-VII-2-11  B-VII-2-19  B-VII-2-20                                                |

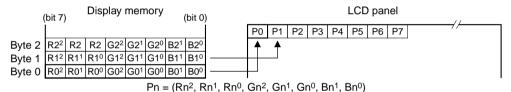

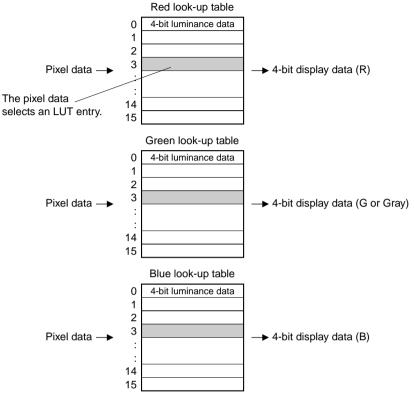

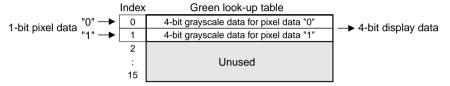

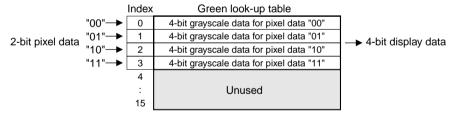

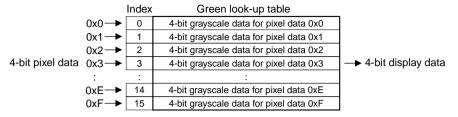

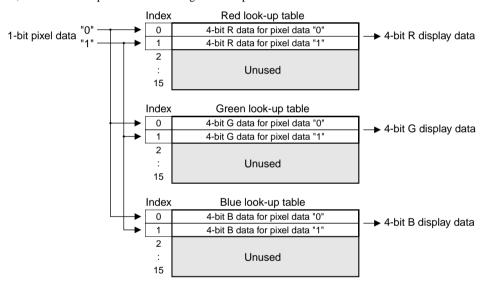

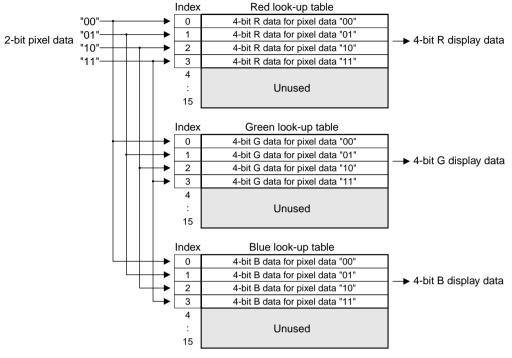

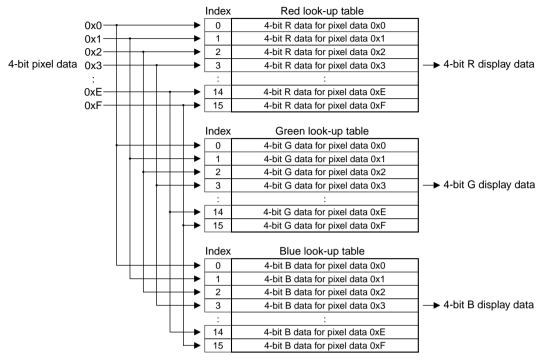

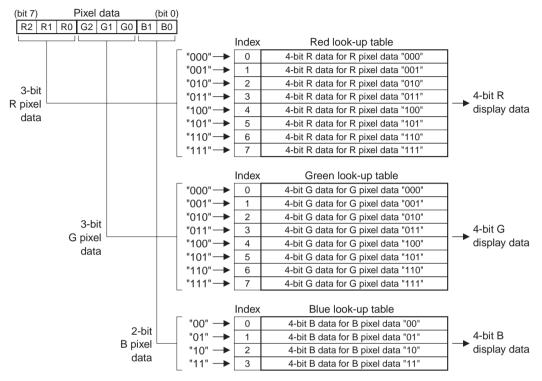

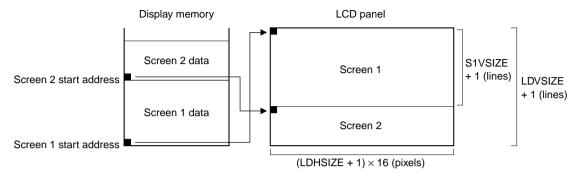

| VII-1 | Examples of SDRAM Controller Initialization Program  CD CONTROLLER BLOCK  INTRODUCTION  LCD CONTROLLER  Overview  Features  Block Diagram  I/O Pins of the LCD Controller  System Settings  Setting the BCU  Display Memory  LCD Controller Setting Procedure  Clock  Setting the LCD Panel  Types of Panels  Resolution  Display Modes  Look-up Tables  Frame Rates | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-3  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-7  B-VII-2-8  B-VII-2-8  B-VII-2-9  B-VII-2-11  B-VII-2-19  B-VII-2-20  B-VII-2-20                                    |

| VII-1 | Examples of SDRAM Controller Initialization Program                                                                                                                                                                                                                                                                                                                  | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-3  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-8  B-VII-2-8  B-VII-2-9  B-VII-2-9  B-VII-2-11  B-VII-2-19  B-VII-2-20  B-VII-2-21                                    |

| VII-1 | Examples of SDRAM Controller Initialization Program  LCD CONTROLLER BLOCK  INTRODUCTION                                                                                                                                                                                                                                                                              | B-VII-1-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-1  B-VII-2-3  B-VII-2-4  B-VII-2-5  B-VII-2-5  B-VII-2-6  B-VII-2-7  B-VII-2-8  B-VII-2-8  B-VII-2-9  B-VII-2-11  B-VII-2-19  B-VII-2-20  B-VII-2-21  B-VII-2-21  B-VII-2-21 |

## **TABLE OF CONTENTS**

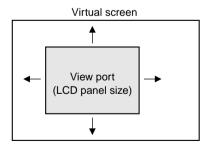

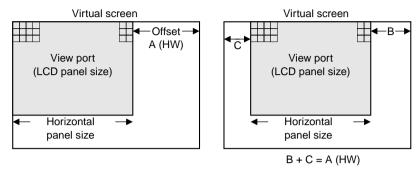

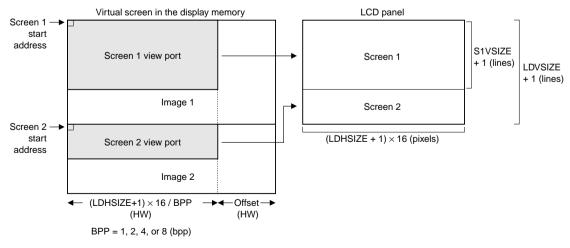

| Virtual Screen and View Port               | B-VII-2-23 |

|--------------------------------------------|------------|

| Inverting and Blanking the Display         | B-VII-2-25 |

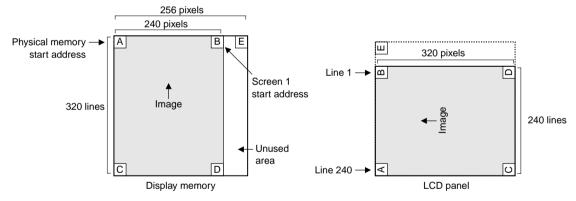

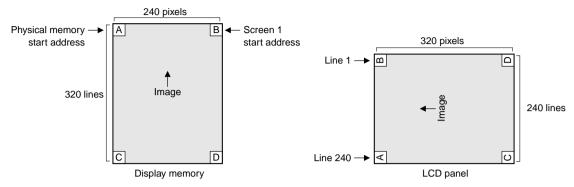

| Portrait Mode                              | B-VII-2-25 |

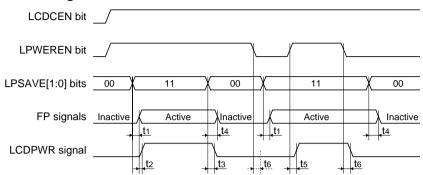

| Power Save                                 | B-VII-2-29 |

| Controlling the GPIO Pins                  | B-VII-2-30 |

| I/O Memory of LCD Controller               | B-VII-2-31 |

| Programming Notes                          | B-VII-2-42 |

| Precautions on Using ICD33                 | B-VII-2-42 |

| Examples of LCD Controller Setting Program | B-VII-2-43 |

## APPENDIX I/O MAP

# S1C33L03 PRODUCT PART

# 1 Outline

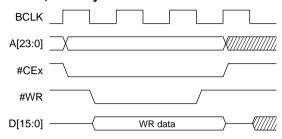

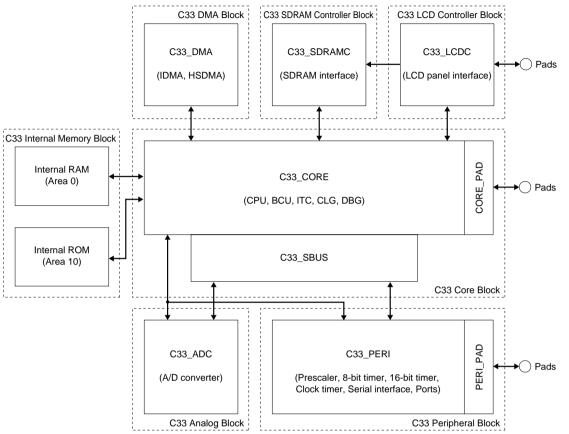

The S1C33L03 is a Seiko Epson original 32-bit microcomputer with a built-in LCD controller. It features high speed, low power and low-voltage operation and is most suitable for portable equipment that needs display function, such as information terminals, E-mail terminals, electronic dictionaries.

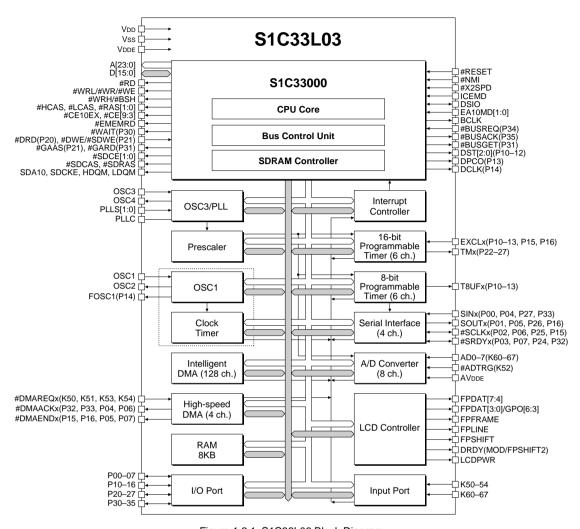

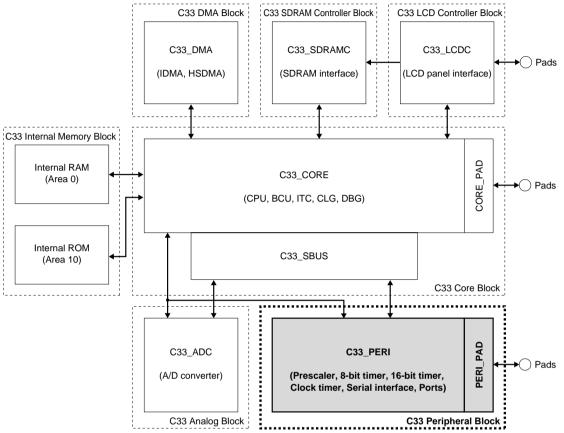

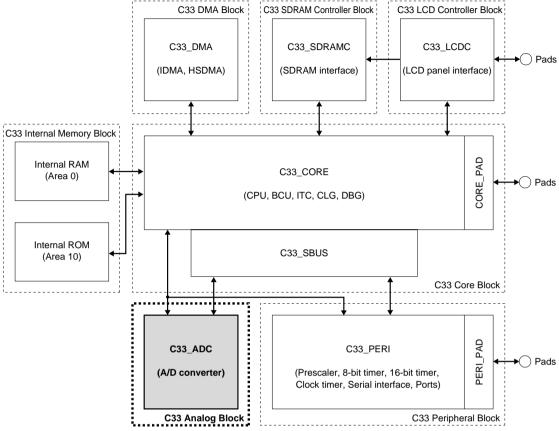

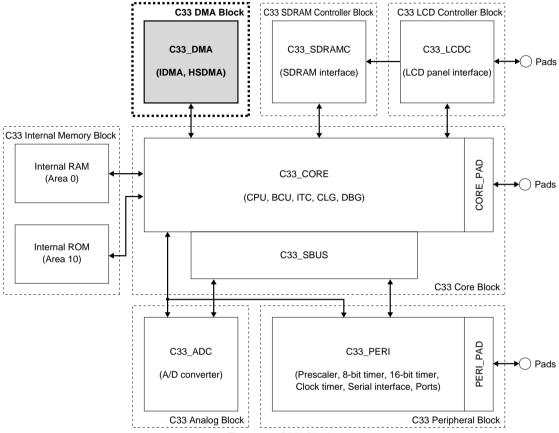

The S1C33L03 consists of the S1C33000 32-bit RISC type CPU as the core, a bus control unit, a DMA controller, an interrupt controller, an LCD controller, an SDRAM controller, timers, serial interface circuits, an A/D converter, ROM and RAM.

The S1C33L03 provides a DSP function, by using the internal MAC (multiplication and accumulation) operation function with the A/D converter, it makes it possible to design simply speech recognition and voice synthesis systems.

Table 1.1 Model Lineup

| Model           | Package                           | Internal RAM | Internal ROM | Data bus I/F |

|-----------------|-----------------------------------|--------------|--------------|--------------|

| S1C33L03F00A100 | QFP20-144pin                      | 8K bytes     | None         | CMOS/LVTTL   |

| S1C33L03F00A200 | QFP20-144pin<br>(Pb-free package) | 8K bytes     | None         | CMOS/LVTTL   |

| S1C33L03D00A100 | Chip                              | 8K bytes     | None         | CMOS/LVTTL   |

## 1.1 Features

## Core CPU

Seiko Epson original 32-bit RISC CPU S1C33000 built-in

- Basic instruction set: 105 instructions (16-bit fixed size)

- Sixteen 32-bit general-purpose register

- 32-bit ALU and 8-bit shifter

- · Multiplication/division instructions and MAC (multiplication and accumulation) instruction are available

- 20 ns of minimum instruction execution time at 50 MHz operation

## Internal memory

RAM: 8K bytes

## Internal peripheral circuits

Oscillation circuit: High-speed (OSC3) oscillation circuit 33 MHz max.

Crystal/ceramic oscillator or external clock input

Low-speed (OSC1) oscillation circuit 32.768 kHz typ.

Crystal oscillator or external clock input

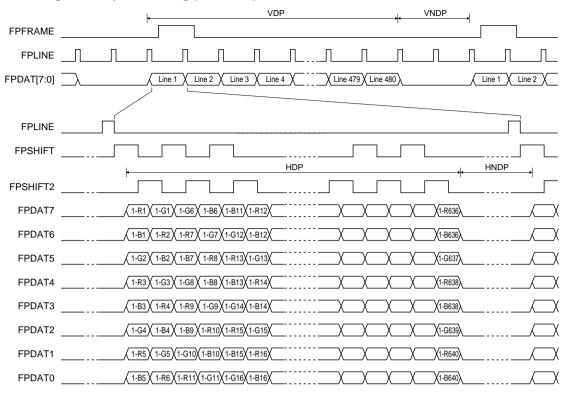

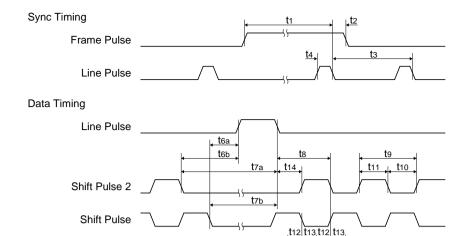

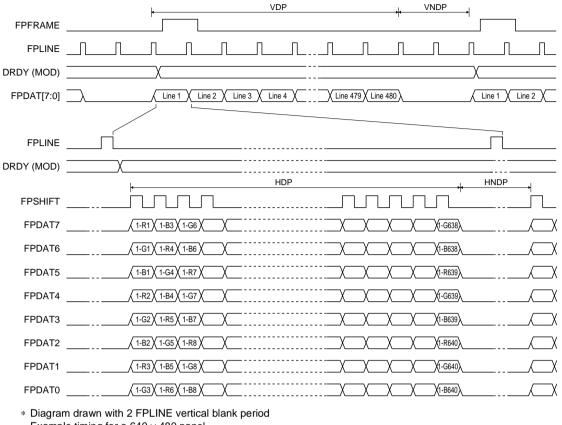

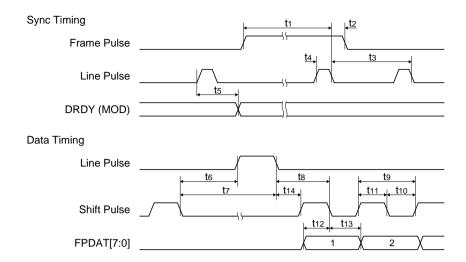

LCD controller: 4 or 8-bit monochrome/color LCD interface (based on the S1D13705)

2, 4 or 16-level (1, 2 or 4 bit-per-pixel) gray-scale display 2, 4, 16 or 256-level (1, 2, 4 or 8 bit-per-pixel) color display Resolution examples: 640 × 480 pixels with 1-bpp color depth

$640 \times 240$  pixels with 2-bpp color depth  $320 \times 240$  pixels with 4-bpp color depth

$240 \times 160$  pixels with 8-bpp color depth

Timers: 8-bit timer 6 channels 16-bit timer 6 channels

Watchdog timer (16-bit timer 0's function)

Clock timer 1 channel (with alarm function)

Serial interface: 4 channels (clock-synchronous system, asynchronous system and IrDA

interface are selectable)

A/D converter:  $10 \text{ bits} \times 8 \text{ channels}$

DMA controller: High-speed DMA 4 channels

Intelligent DMA 128 channels

Interrupt controller: Possible to invoke DMA

Input interrupt 10 types (programmable)

DMA controller interrupt 5 types

16-bit programmable timer interrupt 8-bit programmable timer interrupt 4 types

Serial interface interrupt 6 types

A/D converter interrupt 1 type

Clock timer interrupt 1 type

General-purpose input Shared with the I/O pins for internal peripheral circuits

and output ports: Input port 13 bits I/O port 29 bits

## **External bus interface**

BCU (bus control unit) built-in

- 24-bit address bus (internal 28-bit processing)

- · 16-bit data bus

Data size is selectable from 8 bits and 16 bits in each area.

- Little-endian memory access; big-endian may be set in each area.

- · Memory mapped I/O

- · Chip enable and wait control circuits built-in

- DRAM direct interface function built-in Supports fast page mode and EDO page mode.

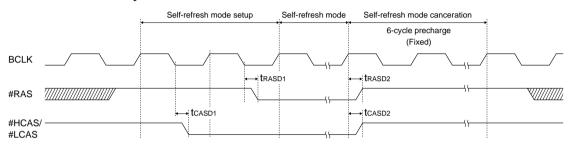

Supports self-refresh and CAS-before RAS refresh.

- Supports SDRAM. Supports SDRAM self-refresh.

- · Supports burst ROM.

## Operating conditions and power consumption

Operating voltage: Core (VDD) 1.8 V to 3.6 V

I/O (VDDE) 1.8 V to 5.5 V

Operating clock frequency: CPU operating clock frequency

50 MHz max. (core voltage =  $3.3 \text{ V} \pm 0.3 \text{ V}$ )

LCD controller operating clock frequency

25 MHz max. (core voltage =  $3.3 \text{ V} \pm 0.3 \text{ V}$ )

\* When the SDRAM controller is used

(core voltage =  $3.3 \text{ V} \pm 0.3 \text{ V}$  and PLL is used),

In x1 speed mode: CPU = Bus = 25 MHz max.

In x2 speed mode: CPU = 35 MHz max., Bus = 17.5 MHz max.

Operating temperature: -40 to 85°C

Power consumption: During SLEEP 3.5 µW typ. (3.3 V)

During HALT 100 mW typ. (3.3 V, 50 MHz) During execution 200 mW typ. (3.3 V, 50 MHz)

Note: The values of power consumption during execution were measured when a test

program that consisted of 55% load instructions, 23% arithmetic operation instructions, 1% mac instruction, 12% branch instructions and 9% ext

instruction was being continuously executed.

## Supply form

QFP20-144pin plastic package, or chip.

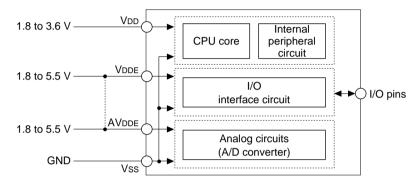

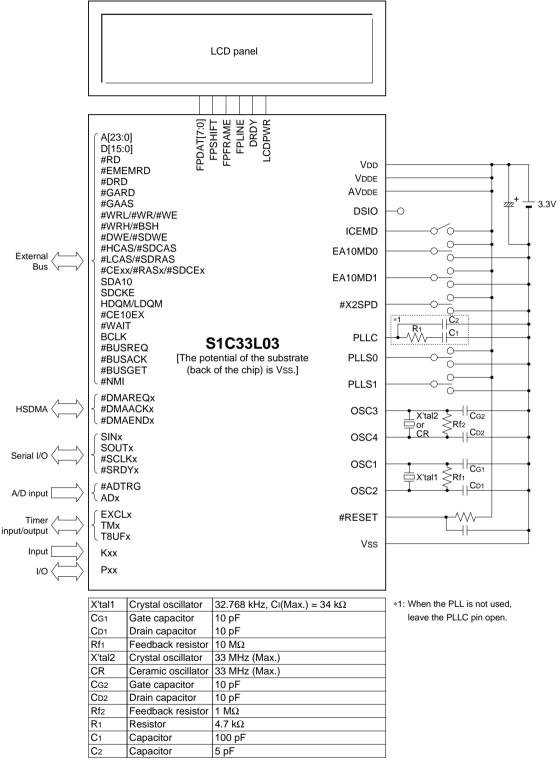

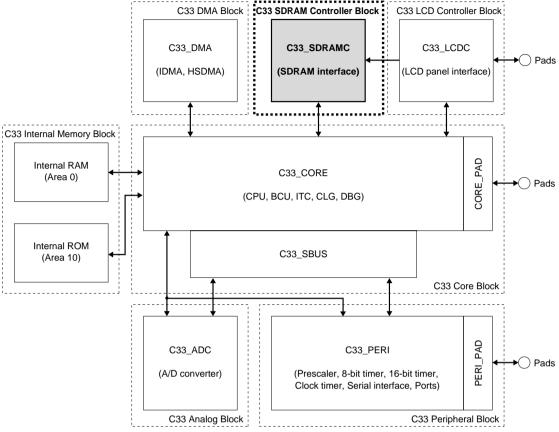

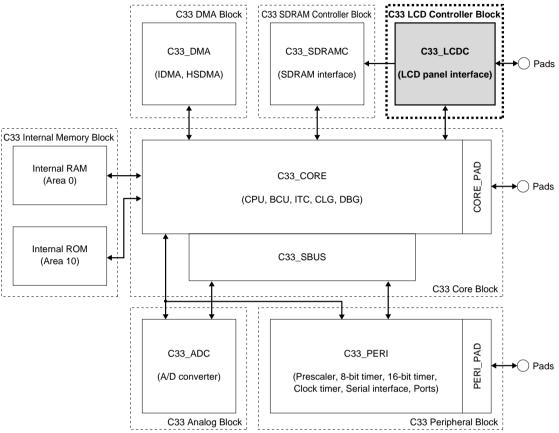

# 1.2 Block Diagram

Figure 1.2.1 S1C33L03 Block Diagram

# 1.3 Pin Description

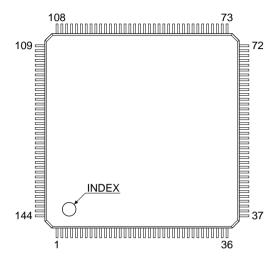

# 1.3.1 Pin Layout Diagram (plastic package)

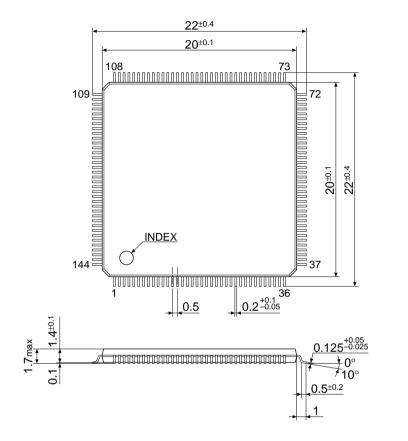

## QFP20-144pin

| No. | Pin name            | No. | Pin name                      | No. | Pin name                       | No. | Pin name             |

|-----|---------------------|-----|-------------------------------|-----|--------------------------------|-----|----------------------|

| 1   | P22/TM0             | 37  | K54/#DMAREQ3                  | 73  | P32/#DMAACK0/#SRDY3/HDQM       | 109 | A21                  |

| 2   | P23/TM1             | 38  | K53/#DMAREQ2                  | 74  | P31/#BUSGET/#GARD/GPIO2        | 110 | A22                  |

| 3   | Vss                 | 39  | K52/#ADTRG                    | 75  | P30/#WAIT/#CE4&5               | 111 | A23                  |

| 4   | P24/TM2/#SRDY2      | 40  | K51/#DMAREQ1                  | 76  | #LCAS/#SDRAS                   | 112 | PLLS1                |

| 5   | P25/TM3/#SCLK2      | 41  | K50/#DMAREQ0                  | 77  | #HCAS/#SDCAS                   | 113 | PLLS0                |

| 6   | P26/TM4/SOUT2       | 42  | #WRH/#BSH                     | 78  | VDD                            | 114 | Vss                  |

| 7   | P27/TM5/SIN2        | 43  | #WRL/#WR/#WE                  | 79  | P21/#DWE/#GAAS/#SDWE           | 115 | PLLC                 |

| 8   | VDD                 | 44  | #RD                           | 80  | P20/#DRD/SDCKE                 | 116 | Vss                  |

| 9   | P07/#SRDY1/#DMAEND3 | 45  | Vss                           | 81  | BCLK/SDCLK                     | 117 | DSIO                 |

| 10  | P06/#SCLK1/#DMAACK3 | 46  | D15                           | 82  | Vss                            | 118 | P14/FOSC1/DCLK       |

| 11  | P05/SOUT1/#DMAEND2  | 47  | D14                           | 83  | P16/EXCL5/#DMAEND1/SOUT3       | 119 | P13/EXCL3/T8UF3/DPCO |

| 12  | P04/SIN1/#DMAACK2   | 48  | D13                           | 84  | P15/EXCL4/#DMAEND0/#SCLK3/LDQM | 120 | P12/EXCL2/T8UF2/DST2 |

| 13  | FPDAT7              | 49  | D12                           | 85  | A0/#BSL                        | 121 | P11/EXCL1/T8UF1/DST1 |

| 14  | FPDAT6              | 50  | D11                           | 86  | A1/SDA0                        | 122 | P10/EXCL0/T8UF0/DST0 |

| 15  | FPDAT5              | 51  | VDD                           | 87  | A2/SDA1                        | 123 | EA10MD1              |

| 16  | FPDAT4              | 52  | D10                           | 88  | A3/SDA2                        | 124 | EA10MD0              |

| 17  | FPDAT3/GPO6         | 53  | D9                            | 89  | A4/SDA3                        | 125 | ICEMD                |

| 18  | FPDAT2/GPO5         | 54  | D8                            | 90  | A5/SDA4                        | 126 | #EMEMRD              |

| 19  | FPDAT1/GPO4         | 55  | D7                            | 91  | VDDE                           | 127 | VDD                  |

| 20  | FPDAT0/GPO3         | 56  | D6                            | 92  | A6/SDA5                        | 128 | OSC4                 |

| 21  | VDDE                | 57  | D5                            | 93  | A7/SDA6                        | 129 | OSC3                 |

| 22  | DRDY(MOD/FPSHIFT2)  | 58  | D4                            | 94  | A8/SDA7                        | 130 | #NMI                 |

| 23  | FPFRAME             | 59  | VDDE                          | 95  | A9/SDA8                        | 131 | #CE9/#CE17/#CE17&18  |

| 24  | FPLINE              | 60  | D3                            | 96  | A10/SDA9                       | 132 | VDDE                 |

| 25  | FPSHIFT             | 61  | D2                            | 97  | A11                            | 133 | #CE5/#CE15/#CE15&16  |

| 26  | LCDPWR              | 62  | D1                            | 98  | Vss                            | 134 | N.C.                 |

| 27  | Vss                 | 63  | D0                            | 99  | A12/SDA11                      | 135 | #CE3                 |

| 28  | K67/AD7             | 64  | #CE8/#RAS1/#CE14/#RAS3/#SDCE1 | 100 | A13/SDA12                      | 136 | VSS                  |

| 29  | K66/AD6             | 65  | #CE7/#RAS0/#CE13/#RAS2/#SDCE0 | 101 | A14/SDBA0                      | 137 | #CE10EX/#CE9&10EX    |

| 30  | K65/AD5             | 66  | Vss                           | 102 | A15/SDBA1                      | 138 | #CE6/#CE7&8          |

| 31  | K64/AD4             | 67  | OSC2                          | 103 | A16                            | 139 | #CE4/#CE11/#CE11&12  |

| 32  | K63/AD3             | 68  | OSC1                          | 104 | A17                            | 140 | #X2SPD               |

| 33  | K62/AD2             | 69  | #RESET                        | 105 | Vss                            | 141 | P03/#SRDY0           |

| 34  | K61/AD1             | 70  | P35/#BUSACK/GPIO1             | 106 | A18                            | 142 | P02/#SCLK0           |

| 35  | K60/AD0             | 71  | P34/#BUSREQ/#CE6/GPIO0        | 107 | A19                            | 143 | P01/SOUT0            |

| 36  | AVDDE               | 72  | P33/#DMAACK1/SIN3/SDA10       | 108 | A20                            | 144 | P00/SIN0             |

Figure 1.3.1 Pin Layout Diagram (QFP20-144pin)

## 1.3.2 Pin Functions

Table 1.3.1 List of Pins for Power Supply System

| Pin name        | Pin No.      | I/O | Pull-up | Function                                     |

|-----------------|--------------|-----|---------|----------------------------------------------|

| V <sub>DD</sub> | 8,51,78,127  | ı   | _       | Power supply (+) for the internal logic      |

| Vss             | 3,27,45,66,  | -   | _       | Power supply (-); GND                        |